Synopsysは10月14日、プロセッサIPコア「ARC HS」ファミリの新製品として、32ビットプロセッサコアの「DesignWare ARC HS38」を発表した。

同製品は、従来の「HS34/36」プロセッサと同様、電力効率(DMIPS/mW)と面積効率(DMIPS/mm2)を追求したアーキテクチャで、組み込みLinuxや他のハイエンドOSをサポートする機能を搭載している。「HS38」が有する処理性能と低消費電力特性は、ホームルータ/ゲートウェイ、データセンター、デジタルTVネットワーク機器、車載インフォテイメント機器といったデバイスで需要が拡大している組み込み制御/信号処理機能の実現にとって理想的であるという。

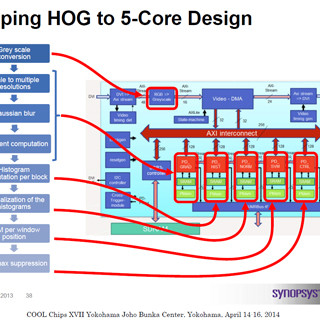

具体的には、「ARC HS」ファミリは、次世代のARCv2 Instruction Set Architecture(ISA)を採用しており、低消費電力/小面積でありながら高性能な組み込みデザインを実現できる。今回の「HS38」は、最大1.93DMIPS/MHzという高い性能効率を提供する他、一般的な28nmプロセスで、消費電力を90mW以下、面積をわずか0.21mm2に抑えつつ、2.2GHzという動作性能を実現する。この時の処理性能は4200DMIPSで、これはLinuxをサポートする前世代プロセッサ「ARC 770D」コアの2倍に当たるという。さらに、40ビットフィジカルアドレススペースと最大16MBのページサイズをサポートするフル機能のメモリ管理ユニット(MMU)を搭載しているため、高速なデータアクセスとより高いシステムパフォーマンス、およびTB級のメモリに直接アクセスする能力を備えている。そして、「HS38」は、マルチコア(2または4個)構成も可能で、SMP Linux、フルレンジの1次キャッシュコヒーレンシおよび最大8MBの2次キャッシュをサポートしている。加えて、オプションの浮動小数点ユニットにより、単精度および倍精度の算術演算命令で計算を加速できる。また、他のARCプロセッサと同様に、コンフィギュアビリティの高いアーキテクチャとなっているため、開発対象のデザインに最適なハードウェア特性を得られる。この他、拡張性も高いためプロセッサと緊密に統合した独自ハードウェアアクセラレータの開発も容易になる。

また、「ARC」ファミリ向け組み込みソフトウェアの開発、デバッグ、最適化を支援する「DesignWare ARC MetaWare Development Toolkit」は、「ARC HS38」もサポートしている。「MetaWare Toolkit」は、非常に処理効率の高いコード生成を実行するC/C++コンパイラ、ソフトウェア内部の観測性を最大限に高めるデバッガ、ハードウェア完成前のソフトウェア開発のためのインストラクションセットシミュレータ(ISS)を提供する。さらに、プロセッサとペリフェラルで構成する「ARC HS Processor Family Virtualizer Development Kit(VDK)」を活用すれば、SoCが完成する前段階から仮想プロトタイプ上でソフトウェアの実行、デバッグを行うことができ、完全サイクル精度シミュレータで、デザインの最適化と検証を実行できる。加えて、「HS38」プロセッサ向けオープンソースソフトウェアとしては、最適化されたLinuxカーネル、GNU Compiler Collection(GCC)、GNU Project Debugger(GDB)や関連するGNUプログラミングユーティリティなどがある。

なお、「ARC HS38」、「ARC HS Family VDK」は、12月の一般提供開始を予定している。さらに、同社のLynx Design Systemへの「ARC HS38」プラグインも12月の提供開始を予定しており、チップレベル統合と最適化にかかる期間を短縮するため事前にチューンナップ済みのデザインフロースクリプト、制約条件、ツールセッティングを提供するという。MetaWare Development Toolkit、Linuxカーネルはすでに提供が開始されている。