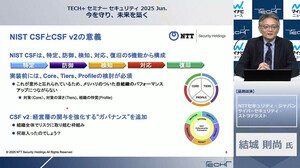

米Lattice Semiconductorは米国時間の4月10日にECP5ファミリーFPGAを発表した。この新ファミリーに関する説明会が前日に日本法人であるラティスセミコンダクターで開催されたので、まとめて御紹介したいと思う(Photo01,02)。

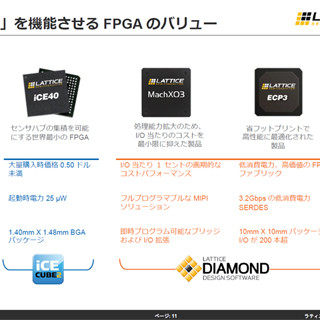

今回発表されたのは、同社の中でコネクティビティやビデオ・イメージング向けという位置づけにあるECP5ファミリーである。同社の中ではハイエンド製品に位置づけられるが、業界的に言えばエントリー~ミッドレンジに相当するもので、実際LUT数だけみればAlteraのCycloneとかXilinxのArtixと同規模になる(Photo03)。

|

|

Photo03:ローエンドがice40シリーズ、ミドルレンジが2014年1月に256Ball Packageが追加されたMachXO3となる。ちなみにice40は元々、同社が買収したSiliconBlueの製品群である |

実は同社は過去に、ECP4という製品のアナウンスを一度行っている。この製品、もしリリースされていればECP5を超えるスペック(LUTの数もトランシーバの速度もECP5を上回る)だったのだが、吉田氏によれば「製品化の途中でちょっとダッチロール状態になってしまい、開発を中止した」との事。今回は改めて製品ターゲットを絞り込んで製品を作り直したが、過去のECP4の型番を使うと混乱するから、ということでこれをスキップしてECP5としたそうである。

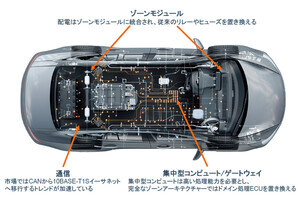

さてそのECP5のターゲットであるが、同社の製品ポリシーは「低消費電力・低価格なFPGAを提供してゆく」事であり、なので他のFPGAベンダーと異なり、Emergingではあるが、小型・低価格市場向けとしている(Photo04)。

あるいは、ASICやASSPのコンパニオンチップとしてのFPGA(Photo05)も主要なターゲットの1つだとする。こうしたASICやASSPのコンパニオンは、かつてAlteraやXilinxも通ってきた道ではあるが、そこを引き続き主要なマーケットと考えているのが同社の戦略である。

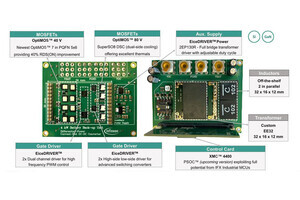

具体的な特徴としては、同一規模のLUTを持つFPGA同士で比較すると最大40%安く、同一速度のSerDesで比較すると30%低消費電力、かつ同一実装面積で比較すると2倍の回路規模であるとしている(Photo06)。ちなみにSerDesは最大3.125Gbpsで、PCIe Gen1にマッチする性能である。

具体例としてSmallcell基地局の構成を考えた(Photo07)とき、すでに主要なコンポーネントはASICやASSP、Discreteで市場に出ている。ただDFE(Digital Front End)周りはキャリア毎に要求が異なるといったケースでカスタマイズが必要であり、その部分をECP5を利用することでトータルコストを安く抑え、開発期間を短縮できるといったケースや、低消費電力の監視カメラユニットをFPGA1個で賄う例(Photo08)、あるいはSFPモジュール内に実装する例(Photo09)などが示された。

|

|

|

Photo07:判りにくいが「40%低コスト」はあくまでFPGAのみの話。全体としてみると、部品コストよりもむしろ開発期間とか開発工数が主要なコスト要因になるから、ここをASIC/ASSPを使うことで低く抑えやすい、という事になる |

Photo08:ここでCPUは、同社が提供するMico32というフリーのCPUコアを想定しているそうだ。ただISPやH.264のEncoderなどは3rd Partyのものとなるとか |

|

|

|

Photo09:普通はSFPの中にFPGAまでは入れられないので、外部にFPGAを使って回路を実装するかたちになるが、ECP5だとぎりぎりSFPモジュール内に収める事が可能になる |

Photo10:従来だとice40クラスでないとここには入りきらなかったが、ice40だと今度はSerDesが無いし、OAM機能を実装するにはややロジックが不足していた |

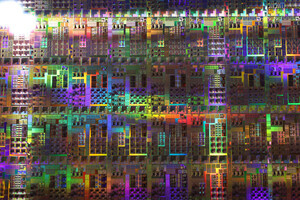

こうした要件を満たすためにECP5はどう工夫をおこなったか、がこちら(Photo11)。製造プロセスそのものはUMCの40nmを利用しているが、まず配線をある程度制限し、また速度も比較的控えめに抑えることで消費電力の削減と実装密度向上を実現したとしている。

|

|

Photo11:ちなみに40nm世代は同社としては2番目(最初の製品はice40)。1月の記者会見でCEOのBillerbeck氏は、当分の間は同社はこの40nmプロセスを使い続けることを明らかにしている |

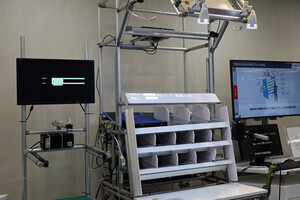

またDSPというか18bitのMACユニットは28~156個搭載しているが、これは今回改めて作り直したもので、例えば必要なら倍速動作をさせることで、見かけ上倍の数を利用するといった事も可能としている。またSerDesは同社のオリジナル(元はAMDから分社化したVantisが開発していたものらしい。Vantisは1999年にLatticeに買収されている)で、これも省電力化に貢献しているとする。実際に、ビデオの形であるがECP5を搭載した開発ボードをPCに装着し、これが概ね0.25Wで動作するというデモも示された(Photo12)。

|

|

Photo12:ビデオそのものは同社の製品ページの右上のサムネイルから見る事が可能 |

そのECP5であるが、現在はαカスタマへのサンプル出荷を開始しているとの事(Photo13)。開発ツールのLattice Diamondは現行バージョンは3.1で、このままではECP5はサポートできない(ECP5のサポートは6月に予定しているバージョン3.2から)が、先行して開発を行いたいユーザー向けにDesign Guideを提供するとの事。またECP5のサンプルを入手しているユーザーにはαバージョンのDiamondバージョン3.2の提供も行うという話であった。

このDiamondは、SerDes無し版は無料提供のものが使えるが、SerDesあり版は有償提供(菅原氏によれば「お安いです」との事)のものが必要ということだった。また開発ボード(Photo14)も用意される。ECP5そのものの量産出荷は8月を予定しており、気になる価格は、例えば100万個発注時であれば5ドル位ではないかとの事。大雑把に言えば1ドルあたり5K LUTを目指すという話であった。