富士通研究所は3月21日、CPU間の大容量データ伝送を実現するために必要な光送受信器用のシリコンフォトニクス技術を用いた4波長集積レーザを開発したと発表した。

詳細は、3月17日~21日に米国アナハイムで開催された「The Optical Fiber Communication Conference and Exposition and the National Fiber Optic Engineers Conference(OFC/NFOEC 2013)」で発表された。

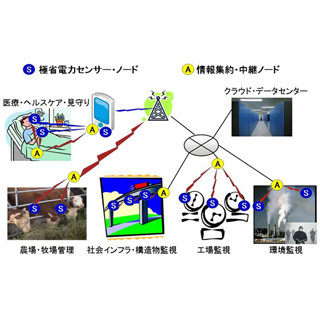

近年、スーパーコンピュータ(スパコン)やハイエンドサーバの演算処理速度は1年半で約2倍のペースで高速化しており、2018年頃には毎秒数テラビットのデータを入出力するための大容量データ伝送技術が必要となると予測されている。そのため、CPU間を光で接続する光インターコネクト技術の適用が検討されており、中でもシリコンフォトニクス技術を用いた光送受信器の開発が注目を集めるようになってきている。

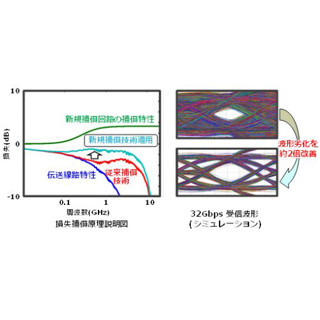

CPU間で大容量データの伝送を行うためには、1本の光ファイバに複数の異なる波長の信号をより多く束ねること(多重化)が有効となるため、シリコンフォトニクス技術においても波長多重化技術が開発されている。従来は、サイズの異なるリング共振器を用いて、各波長(ch1~4)を生成していたが、各波長を決めるリング共振器の周回長が製造バラつきのために設計値からずれやすいほか、各波長の間隔が狭いため環境温度変動によって波長の変化が生じた場合、各波長の識別ができなくなるという問題があった。また、環境温度が変化することに伴って生じる波長変化を補正するため、波長ごとに温度調整回路が必要になるなど装置が複雑化していたほか、各信号を合成、分離する際の損失を補うために信号を高出力化する必要があった。

そうした課題の解決に向け同社は今回、リング共振器が持つ周期的な透過特性を利用して各波長を広い間隔で均一に生成することに成功したほか、シリコン基板上の複数の光配線と光増幅素子を高精度に接続する実装技術により接続時の損失を低減。これらにより、12±0.5nmの均一な波長間隔の4波長で発振し、出力+5dBmのシリコン集積レーザを実証したという。

今回開発された技術としては、「レーザ発振波長制御技術」と「低損失光増幅器結合技術」がある。レーザ発振波長制御技術は、複数の異なる波長の信号を広い間隔で均一に生成する技術。各レーザは、4つの同じサイズのリング共振器で構成され、各リング共振器は周期的な透過特性を持つ波長フィルタとして動作する。また、各リング共振器には周期的な波長の中から1つを選択するよう波長選択機構(DBRミラー)が設けられており、それぞれが異なる波長を選択することで4波長を生成する。

今回の構成では、各リング共振器は同じサイズで構成されており周期特性が同一のため、各波長の間隔は従来のようにリング共振器の周回長の差分ではなく、リング共振器が持っている周期特性で決まり、各レーザの動作波長を等間隔で精度よく生成することができる。また、今回の構成と同じサイズのリング共振器を用いた変調器と組み合わせることで、温度変化による波長の変動をキャンセルすることが可能なため、CPUパッケージのような環境温度が変化する時にも、消費電力が大きい温度制御回路を必要とせずに光送信器を構成できる。

一方の低損失光増幅器結合技術は、光増幅素子をシリコン上に高精度に搭載する技術。4チャネルの光増幅素子をシリコン上の光導波路に誤差±0.5μm以内で高精度に直接貼り合わせて搭載することで、光増幅素子とシリコン共振器の接続時の損失を低減し、4波長シリコン集積レーザで、波長多重光通信に十分な+5dBm以上の光出力を得ることに成功したという。

今回の技術を用いた光送信器を1チップに多数集積することにより、CPUモジュールに搭載可能なサイズながら毎秒数テラビット級の光データ伝送が可能となることから、同社では今後、さらに研究を進め、シリコンフォトニクス技術を用いた波長多重に対応した光受信器を開発し、今回開発した光送信器と集積することで小型光送受信器の実現を図っていくほか、大規模集積化や実装技術を開発し、CPUパッケージに搭載する毎秒数テラビット級の大容量、小型の集積光インターコネクトの開発を進めていく計画としている。