NVIDIAは、2月25日から開幕するスペイン・バルセロナで開幕する「Mobile World Congress 2013」に先立ち、米国時間の2月24日、同社の最新モバイルプロセッサ「Tegra 4ファミリー」の詳細情報を公開した。Tegra 4ファミリーは、今年1月に発表された開発コードネーム"Wayne"(ウェイン)で知られる高機能スマートフォン/タブレット向けの「Tegra 4」と、先週同ファミリーのエントリーモデルとして発表された開発コードネーム"Grey"として知られるメインストリームスマートフォン向けの「Tegra 4i」の2製品から構成される。

■先週公開された「Tegra 4i」のレポートはこちら

・【レポート】米NVIDIA、"A15"じゃない「Tegra 4i」を公開 - 100ドル台スマホ向け、Cortex-A9ベースでLTEモデム統合

http://news.mynavi.jp/articles/2013/02/19/tegra4i/

既報のとおり、この両製品は、統合するCPUコアの種類やグラフィックスの構成が異なっていることが明らかになっているが、公開された詳細資料からは、Tegra 4に統合されたグラフィックスコアは、Terga 3から大きくアーキテクチャ変更が施されていることや、異なる半導体製造プロセス技術を採用することで、省電力性とパフォーマンス向上のバランスを採っていることも明らかになった。

Tegra 4の概要

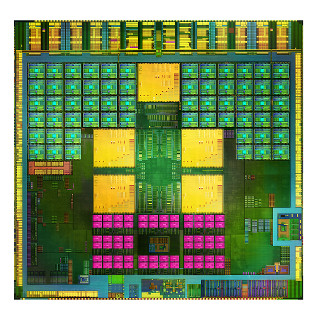

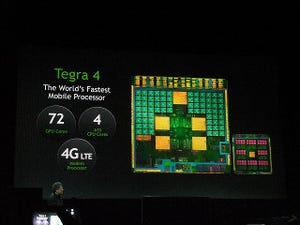

Tegra 4ファミリーのフラグシップとなる"Wayne"こと「Tegra 4」は、CPUコアにARMの最新コア「Cortex-A15」を採用し、省電力動作を実現するバッテリーセーバーコアを組み合わせた4+1構成のクアッドコアSoCで、グラフィックスコアはTegra 3の12コアから72コアへと大幅強化されたことが、今年1月の製品発表でアナウンスされた。しかし、今回公開された技術資料からは、CPUアーキテクチャを一新しただけでなく、グラフィックスアーキテクチャにも大きく手が入れられているほか、4+1コアの仕組みにもメスが入れられるなど、大幅な設計変更が施されていることが明らかになった。

Cortex-A15は、Tegra 3に採用されているCortex-A9と同じARMv7命令セットを採用する最新CPUコアで、ARM Cortex-A9の2命令デコード・最大4命令同時発行のアウト・オプ・オーダー実行スーパースカラパイプラインから、3命令デコード・最大8命令同時発行にマイクロアーキテクチャが強化されている。さらに、アウト・オプ・オーダーパイプラインはCortex-A9の8段から、3-12段へと拡張され、より高クロックで動作できるようになっている。

このCortex-A15を4+1構成で搭載するTegra 4は、クアッドコアで共有する2MBのL2キャッシュを備え、最大1.9GHzで動作、DDR3L/LPDDR3-1866に対応するデュアルチャネルメモリインターフェースを採用する。また、NVIDIAはTegra 4の開発にあたり、バッテリーデーバーコアとなるもう一つのCortex-A15コアに専用の512KBキャッシュを用意し、省電力動作時はメインのクアッドコアCPUの電力をOFFにするだけでなく、2MBの共有L2キャッシュもパワーゲーティングにより電力消費を抑えられるようにしているなど、よりアグレッシブな省電力化が図られている。

NVIDIAは、Tegra 4の演算性能をTegra 3と同等になるまでクロックを下げた状態で消費電力を比較したデータなどを公開し、省電力性の高さをアピール。また、最大のライバルとなるQualcommのSnapdragon 800との性能比較データなども公開している。

次ページ:大きく変わったグラフィックス機能