半導体チップの開発、製造の仕組みがわかる展示

博物館のもう1つの主要テーマは、Intelの主要な活動であるチップの開発と製造がどのように行われているかを訪問者に分かって貰うことである。内容は専門家向けではなく、一般の訪問者にも理解できるレベルになっている。

チップの設計については、設計の各ステップに関して、専門家がビデオで解説をしてくれる。また、3次元の多層パネルを使って、配線やビアの接続を示す展示も設けられている。

そして、チップの製造に関しては、まず、原料となるシリコンインゴットとウェハが展示されている。余談であるが、丸いウェハ上に四角いチップを作るとフチが無駄になるので四角いウェハの方が良いのではないかと言った人がいるが、元々のシリコンインゴットは種結晶を回転させながら引き上げて作るので、この写真に見られるように円柱にしか作れない。この円柱から四角いウェハを切りだすとムダが大きくなってしまうので、ウェハは円形になっている。

右は歴史的なウェハの展示で、右上はIntel創業直後の1969年に使われた2インチ(50mm)ウェハで、1972年の3インチ、1976年の4インチ、1983年の6インチ、1993年の8インチと拡大し、現在は、左側の300mm(12インチ)ウェハが使われている。

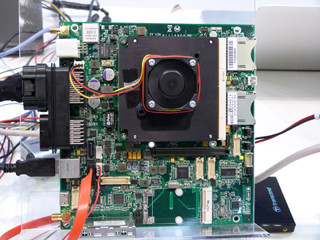

そして、このウェハに、チップの設計に基づいて、トランジスタや配線を作り込んでいく過程と半導体の製造を行う工場(FAB)の説明が続いている。「How Intel Makes Chips」という展示では、トランジスタの拡散領域を作るイオン注入から、High-K絶縁膜の形成、ゲートの形成、配線の形成、ウェハテストとダイシング、パッケージングと最終テストと一連のチップ製造過程が説明されている。

製造工場は4階建てで、一番上はファンデックという階で、ミクロン以下の目の細かいフィルタでほこりを除去し、適切な温度に調節した空気を作って製造装置があるクリーンルーム階に送り出す役目を担っている。

そして、オレンジ色の光に照らされている階がクリーンルームという階で、ここにチップを作る各種の製造装置が並んでいる。半導体チップ上に色々なパターンを作るために感光樹脂が使われるが、この樹脂を感光させないようオレンジ色の照明が使われている。上階のファンデックで作られた清浄な空気は、クリーンルームの天井から床に向かって一様に流れていて、クリーンルーム内でほこりが発生しても、この空気流に乗って床に吸い込まれ、室内の空気を清浄に保っている。

クリーンルームの下の白色照明の階はクリーンサブファブと呼ばれる階で、クリーンルームの製造装置に、製造に使われる各種のガスや、液体などを供給する。最下階はユーティリティ階で、電気を供給したり、空気や水を循環させるダクトなどが設置されている。

微細なトランジスタや配線を作り込む半導体ウェハは、小さなほこりの粒子が付着しても、その部分が不良品になってしまう。このため、ファンデックでは1μmより小さなほこりもフィルタで取り除く。しかし、クリーンルームの中で働く人から、ほこりが落ちたのでは清浄度が保てない。このため、ヘアネットや靴のカバー、手袋などをつけ、さらに、バニースーツというカバーオールを着る。これらの着衣は不織布などの、繊維の端がちぎれてほこりを出さない材料で作られている。また、クリーンルーム内ではほこりを発生する普通の紙や鉛筆ではなく、ほこりを発生しないプラスチップのシートやボールペンが使われる。

そして、完成したウェハ上のチップは、ウェハプローブを使ってテストされ、ダイシングソーという丸鋸で切断して、良品チップを取り出す。その後、パッケージに入れられて、再度、試験を行い完成品となる。

そして、完成品には、機器の外側に張るIntel Insideのシールが付けられるが、上の写真のように、実に35種ものシールが展示されていた。