プロセスの微細化により半導体デバイスが搭載できるトランジスタ数は劇的に増加している。近年のCPUなどでは、その増加したトランジスタを通常の汎用処理ではなく分野に特化したアクセラレータとして振り分けることで、全体的な処理性能の向上を図るなどの動きを見せているが、そうしたトランジスタ数の増加は、これまでインタフェースなどのシステムLSIやCPUの周辺を担当していたFPGAにハイパフォーマンスなプロセッサを搭載する余地を与えるようになり、その結果、プロセッサやインタフェースなどを含んだFPGAがシステムLSIなどから置き換わろうとしている。

FPGA大手のXilinxはZynqシリーズという名称で、同じく大手のAlteraもSoC FPGAという名称で、そうした戦略を取り始めた。特にAlteraは、これまでシステムの中央はCPUなどで、その周辺をFPGAが担うとしていたが、ここに来て、大きな舵取りの変化をしようとしている。同社の今後のFPGAの方向性などについて、同社Senior Vice President & CTOのMisha Burich氏に話を聞く機会をいただいたので、その中から、同社が狙う将来のFPGAの姿などについてお伝えしたい。

こうした動きはプロセスのシュリンクによるASICの設計・製造コストの肥大化とFPGAのダイサイズの縮小が顕著になってきたからだ。ダイサイズで言えば、40nmプロセスを採用したAlteraのFPGA「Stratix IV」は130nmプロセスを採用したASICと同規模になり、搭載ロジックエレメント数も2000年ころに500K LEを超え、DSPやASSP、ASICの置き換えがネットワーク領域などで可能となってきた。そして2010年ころには1M LEを超え、ハイパフォーマンスな汎用プロセッサを活用しやすくなってきており、例えばIntel AtomとArria II GXを組み合わせたチップソリューションなども登場するようになってきた。

「こうしたFPGAにマイクロプロセッサやDSP、ASIC、ASSPなどを組み合わせていく"Mixed-System Fabric"を実現していくポイントは、それをどうプログラミングしていくかだ」(Burich氏)であり、システムレベルで活用可能なソリューションへの対応を進めていることを強調する。

現在、同社の最先端FPGA製品はTaiwan Semiconductor Manufacturing(TSMC)の28nmプロセスを活用して生産されている。将来的な話として、次世代プロセスの開発状況としては、詳細は明らかにされなかったが、やはりTSMCと共同開発を進めており、TSMCが予定している次世代プロセスである20nmプロセスが採用される予定だ。

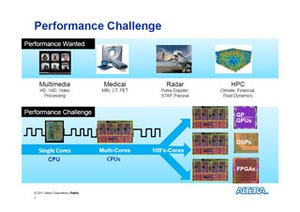

ここでポイントになってくるのが、どこまでFPGAのロジックエレメント(LE)が増大し、その結果、何がFGPAにもたらされるかだ。狙いはASIC/ASSPに代わるシステムの中心であり、そのためにはFPGAがそれらの機能を内包していく必要がある。SoC FPGAでは「従来DSP/MCU+ASIC、および周辺I/Oチップなどで行ってきた処理をDSP/MCU+FPGAのみで、かつ480MIPSの性能を3.2Wで実現可能となった。次世代のPhase2では、DSP/MCU部分もFPGAに内包し、1チップながら1500MIPSの性能を2Wで実現可能となり、50%のBOMコストの低減と大幅な電力の削減が見込めるようになる」(同)とする。

その一方で、「例えばアクセラレータや基本的なI/Oなどをハード的に搭載する可能性もある」とも回答している。同社は2011年にOpenCLを用いたFPGAでの並列コンピューティング処理技術を発表するなど、従来のFPGAの使用補法とは若干異なる方向性の模索を進めているが(FPGAを用いたHPC向けアクセラレータそのものは昔からあったが)、トランジスタ数に余裕があれば、ハード的にそうした機能を搭載してサポートすることも可能となる。

「さまざまのチップの良い部分をFPGAに融合することが可能となってきた。それこそがFPGAの最大の強みであり、"Silicon Convergence"だ」とFPGAにすべての機能が集約されていく様子を表現するが、FPGAにプロセッサを統合しようと思えば、ライセンスが必要となる。「FPGAだけですべてのシステムを実現できると思っていない。IntelやARMとの協業は、そういうことを見越したもので、多くのパートナーと手を取り合い、エコシステムを構築していくことが重要だ」とする。こうなってくると、前述の競合ベンダであるXilinxのZynqシリーズとはどう戦略的に違ってくるのかが疑問に思えてくるが、同氏は「AlteraはASIC化サービス(Hard Copy)を提供してきたが、このナレッジが重要になってくる。FPGAにすべてが入ると言っても、ASICの方が良いというカスタマも多く、そういうカスタマに対しても強みをだせるようになるためだ」と違いを説明する。

こうしたSoC FPGAの取り組みだが、ハイエンドのStratix Vはまだ製品ラインアップに加わっておらず、ミドルレンジ/ローエンドの「Arria V」と「Cyclone V」での提供となっている。「基幹領域などのオペレーションではまだARMコアはパフォーマンスが足りないことが懸念点となっている」とのことであるが、特定カスタマからはすでに要求も出ており、ディスカッションは開始しているとする。

また、次世代技術としてパッケージに光ケーブルがダイレクトにつながり、チップ内部でも一度、銅配線に落とすのではなく、ダイの目の前まで光で届くといった技術の開発を進めていることを2011年に同社は明らかにしたが、すでにプロトタイプのチップは完成しており、何らかの形でのデモの公開なども検討しているというとするほか、TSMCのCoWoS(Chip on Wafer on Substrate)を活用した3Dパッケージ品の開発も進めており、「ヘテロジニアスなFPGA+メモリ(DRAMやSRAM)と言ったものを考えている」とする。

|

|

|

|

|

メタルケーブルを用いることなく光ケーブルをダイレクトにチップに届けることが可能なデモチップ。パッケージ上に光学モジュールを配置し、そこに置かれたフォトダイオードで変換が行われる。光学モジュール部分がパッケージよりも厚みがあるため、ヒートシンクはメインのパッケージ部分と2つの光学モジュールの合計3つが用いられることになるという |

||

「我々のコンセプトはこれまで築いてきたエコシステムの強化を進めていくことだ。効率、使いやすさ、自らが作ってきた部分あるが、パートナー各社に任せている部分も多い。例えばVerilogやVHDLではなくCやC++で開発したいという要望は多いが、こうしたツールはパートナーがやってくれる。しかし、パートナーも経験が不足しているOpenCLなどはまず我々がノウハウの獲得含めてやっていく必要があると思っている」とのことで、そうした意味では年に2回のアップデートを予定している同社の開発ソリューションである「Qurtus II」の進化に期待してもらいたいとしていた。