富士通研究所は4月23日、面積と消費電力を半減できるA/Dコンバータ(ADC)技術を開発したと発表した。

ADCの動作は、一般的に外部から入力されたアナログ信号の値と内部で生成した基準値を比較することで、デジタル値に変換する(図1)。しかし、基準値を生成するために基準電圧発生用抵抗群が必要で、定常的に電流を流す必要があるため省電力化が困難だった。また、基準値を設定するために基準電圧切り替えスイッチが必要となり、半導体の微細化が進むにつれ、このスイッチの高速切り替え性能や、オン時の抵抗値のバラつき性能などを保証することも難しくなっていた。

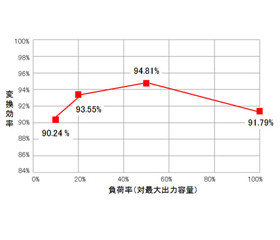

そこで今回、この基準電圧発生用抵抗群や基準値の生成が必要ない、新しいデジタル制御の回路方式を開発。分解能6ビット、変換速度1GS/sの性能を世界最小レベルの実装面積0.04mm2、消費電力9.9mWで実現した他、多チャネル配置して高速動作を実現するタイムインターリーブ動作により数十Gレベルの動作も実現した。これにより、システムの高性能化に繋がるとしている。

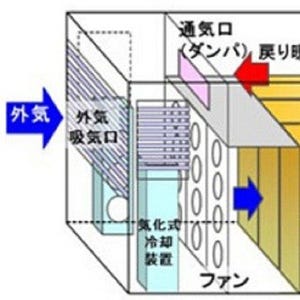

新技術では、比較基準電圧を与える代わりにデジタル値を与え、このデジタル値で制御される比較基準電圧(Vref)相当の基準点とアナログ入力信号の大小を比較するよう動作する(図2)。具体的には、量子化された個別の電流源を電圧比較器内部に配置しておき、実際に電流を流す個数を調整することによって判定レベルを制御する(図3)。

こうすることで、基準電圧発生用抵抗群が不要になり、この抵抗に流れる定常的な電流(約1mA)を削減することができ、また、基準電圧切り替えスイッチが不要となるため高速化も可能となった。

今後、同社では同技術を、サーバを構成するボード間のバックプレーンインタフェースなどへの適用を進めていく。また、さらなる微細化プロセスに適用するとともに、他のアナログ回路にも応用していく考えだ。

なお、同技術の詳細は、4月23日から台湾で開催されている国際会議「2012 VLSI-DAT(2012 International Symposium on VLSI Design, Automation & Test)」にて発表された。