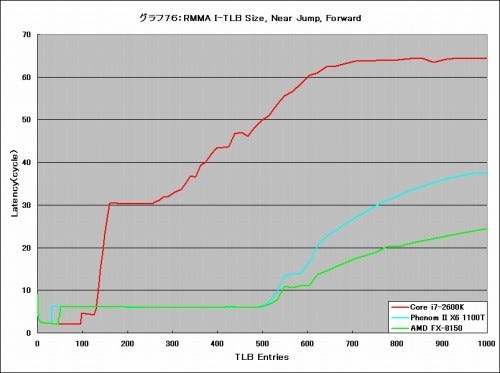

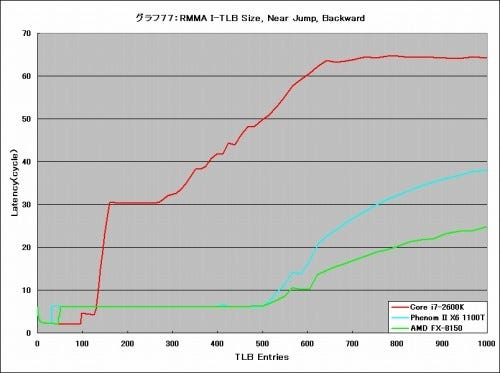

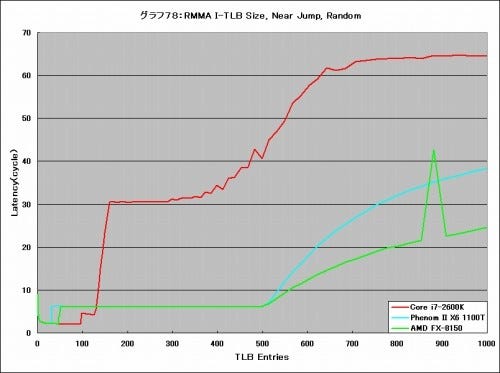

I-TLB(グラフ76~105)

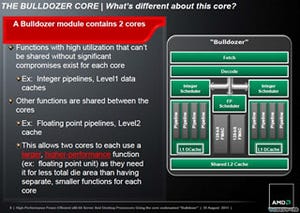

そんなわけでD-TLBは散々だったわけだが、I-TLBはどうか? である。まずI-TLBの構成であるが、Photo01にも在るとおりL1 I-TLBは72 EntryでFully Assosiative、L2 I-TLBは512 Entryで4-way構成となっている。もっともL2に関しては4KB Pageのみの対応で、L1は複数のPage Sizeに対応とあるわけで、結果として4KB Pageの場合は共有L2 TLBはL3 TLBとして働く形になる(4KBを超えるようなLarge Pageの場合、L2 I-TLBはパスされるので、共有L2 TLBがL2 I-TLBとして動く事になる)。

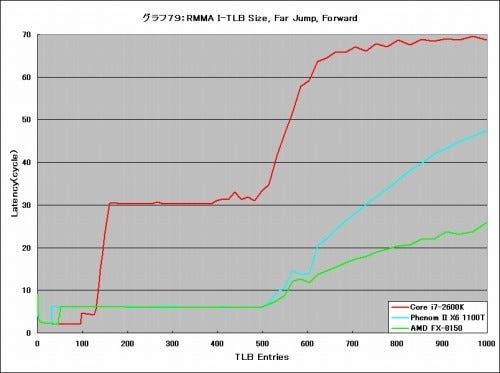

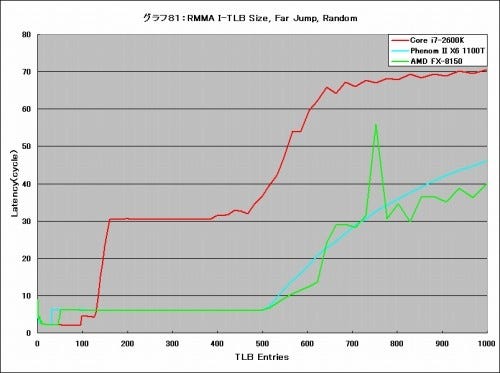

さて、まずはNear Jump(グラフ76~78)とFar Jump(グラフ79~81)でSize Determinationを実施してみた。意外に、というとあれかもしれないがこちらは非常に素性が良い。まずNear Jumpの結果を見ると、50 Entry付近まではLatencyが2 Cycle、その後は53 Entryあたりまで6 Cycleを維持している。その後少しLatencyが増えるが、600 Entry付近まで多少なりとも水平を維持するのはL3 TLB(共有L2 TLB)が効果を及ぼしているためと想像される。それにしても、D-TLBでは随分数字が悪かったのが、I-TLBに関してはかなりLatencyが低いのが、ちょっとミスマッチというかバランス的にどうだろう? という気がする。またグラフ78では、なぜか900 EntryのあたりにいきなりLatencyが急増するSpikeがあるのも謎である。

こうした傾向はFar Jump(グラフ79~81)でも見て取れる。ただBackward(グラフ80)では970 EnrtyあたりからLatencyが急増したり、Random Access(グラフ81)では妙にジグザグになったり、というあたりはやはりまだ熟成不足な部分が残っている様にも思われる。