1つのプロセス/アーキテクチャを複数製品ファミリに展開

|

|

|

Xilinx Sr.Director,Application & Technical MarketingのRina Raman氏 |

Xilinxは6月27日、都内で技術説明会を開催し、同社の次世代FPGA「7シリーズ」の低消費電力技術に関する説明を行った。

7シリーズはTSMCの28nm HPLプロセスと同社のアーキテクチャを組み合わせたもので、「Artix」「Kintex」「Virtex」の3種類の製品ファミリがラインアップとして用意されている。Xilinx Sr.Director,Application & Technical MarketingのRina Raman氏は、「3つの製品ラインアップの提供により、通信インフラから、サーバ、携帯機器に至るまで、幅広い分野で低消費電力化を提供することができ、発熱の抑制やCO2排出量の削減、バッテリ寿命の長期化などを図ることが可能となる」とするほか、「同じリファレンスデザインを用いた場合、Virtex-6とKintex-7では全体の消費電力は6.5W対3.1W、スタティック電力でも3.6W対0.9Wと相当低い結果を達成している。Xilinxが提供するパワーエスティメータツール「XPE(XPower Estimator)」でも3.478Wと実ボードで測定した電力と同程度の測定結果を達成している」とし、前世代FPGAと比べ、いずれのファミリも消費電力を50%低減することが可能となったとする。

同社の競合ベンダであるAlteraは28nmプロセスとしてTSMCの28LPをローエンド品「Cyclone V」とミドルレンジ品「Arria V」に採用し、ハイエンド品「Stratix V」に28HPをそれぞれ採用している。「28HPはGPUに最適化したプロセス、28LPは携帯電話に最適化したプロセス。28HPLはパフォーマンスは28HPに匹敵しつつ、消費電力を28LPに近づけたもので、XilinxはFPGAに適したこのプロセスを3ファミリともに採用した」と、28HPLプロセスを選択した理由を説明する。また、こうした1つのプロセスおよびアーキテクチャをさまざまな製品に展開することについて、「Intelは、1つのアーキテクチャとプロセスを組み合わせることで、それぞれのセグメントに向けたCPUを製造している。こうした手法を用いることで、シームレスにさまざまな分野に対応した製品を柔軟に提供していくことが可能となる」と、その背景にある理由を述べる。

|

|

|

|

Intelには別アーキテクチャでAtomのプラットフォームがあるが、1つのアーキテクチャを複数の製品ラインアップに適用していくのが現在のテクノロジートレンドとするのが同社の主張するところで、7シリーズもそうした1つのアーキテクチャを横展開している製品であることを示したかったとのこと |

|

トータルでの電力削減を重要視

同社が重要視しているのはデバイス全体での電力削減。そのため、7シリーズでは前世代プロセス(45/40nm)品比でスタティック電力を65%低減したほか、ダイナミック消費電力を同25%、I/O消費電力を30%、トランシーバ消費電力を同60%削減することで、全体で50%の低消費電力化を実現しており、「50%の電力削減が可能となったということは、電力を従来と同じだけ消費して良いならば、パフォーマンスを2倍に向上することが可能となることを意味している」とする。

また、7シリーズでは電力低減のためにトランシーバそのものの再設計を行ったことによりトランシーバ消費電力の低減が図られているほか、I/O部分については、メモリ書き込み中に入力バッファ(IBUF)と終端を自動的に無効化する機能を新たに追加。これにより、終端とIBUFのDC電力を書込速度%に比例して、必要に応じて不要な部分から削減することができるようになったことに加え、アイドリングモード時の電力節約のために終端とIBUFをオフにするファブリックアクセスをオプションとして提供することで、さらなる低消費電力化を実現している。

さらに、クロックゲーティングとして、シリコン内の内蔵多層クロック抑制機能を搭載することにより、CEクロックゲーティングが全クロックツリーとロジック電力を削減したほか、出力スイッチングを開発ツール「ISE」にて、不要なスイッチングを抑制することでスイッチングアクティビティ(α)を自動的に低減することが可能であり、これらの機能を活用することで、最大30%、平均18%のロジック電力の削減が図られている。

加えて、メモリの消費電力比率が高いことから、ブロックRAM(BRAM)分野に対し、最適化したイネーブル信号(CE)をBRAMに挿入し、サイクルごとの無効化などを図ることで、最大で70%、平均でも30%のBRAMの消費電力削減を実現したという。

このほか、同社では一般的なコンシューマグレード(C)品としての提供ではなく、「-2LE」と呼ぶCよりも1つ上のグレードとして0~100℃に対応しつつ、リーク電力のバラつき部分(ハイパフォーマンス部分や低リーク部分)を削った形でも提供を行うほか、0.9V動作品を提供することで、さらなる低消費電力を実現できるようになるとする。

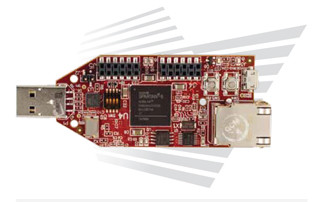

なお、同説明会ではVirtex-6(LX240T)を搭載したものと、Kintex-7(7K325D)を搭載した評価ボードを用いてLabViewによる実際のデモも披露。Virtex-6を立ち上げた状態(ファン停止)で4W程度、回路をFPGAに組み込み、実際に駆動されると6W程度(ファン停止。ファンを回転させると5W程度に低下した)であったのに比べ、Kintex-7の方は、立ち上げ時で1W程度、回路を駆動させた状態でも2.3~2.4W程度でヒートシンクなしの状態で稼働できることが示された。