2011年5月4日、Intelは次世代の22nmプロセスではトライゲート(Tri-gate)トランジスタを採用すると発表した。同Tri-gateトランジスタのプレゼン資料はIntelのWebサイト(注:リンク先はPDF)に公開されている。

これまでの一般的なMOSトランジスタは、図1のようにシリコン基板(Silicon Substrate)上に薄いゲート酸化膜(Gate Oxide)を挟んでゲート電極を設けるという平面構造であったが、今回のTri-gateトランジスタでは図2のように3次元構造に変わる。

Tri-gateトランジスタでは紙面奥行方向に延びているシリコンの薄い板(フィン)があり、それに直行するように少し厚めのゲートと書かれた板状の電極が設けられている。そして、ゲートとシリコンフィンの間には黄色で書かれた薄いゲート絶縁膜がある。つまり、ゲート電極がゲート酸化膜を挟んでシリコンと向かい合っているという基本的な構造は変わっていないのであるが、図2の構造ではゲート電極が薄いシリコンフィンの左右の両面と上の面を囲んでおり、それぞれの面がゲートとして働くのでTri-gateと呼んでいる。

このような3次元構造のトランジスタは1999年にカリフォルニア大バークレイ校のChenming Hu教授のグループからFinFETとして発表されているが、2002年にIntelが発表したTri-Gateトランジスタはシリコンフィンの幅と高さが同じ程度で、非常に薄いシリコンフィンを使うFinFETよりもこの構造の方が製造性が高い。また、FinFETではトランジスタのチャネル幅はフィンの高さの2倍であるのに対してTri-Gateでは上面が加わって3倍になるので、得られるドレイン電流も大きいと主張していた。

しかし、今回発表の図2の模式図を見ると薄いシリコンフィンが使われているようであり、一般的にはFinFETの範疇に入るトランジスタと思われる。なお、今回の発表では、Intelはシリコンフィンの寸法は公表していない。

プレナートランジスタでは、図2のように空乏層(Depletion Region)がシリコン基板の内部に広がるがその下のシリコン基板(Substrate)の電位がトランジスタの電流に影響を与え、これがトランジスタがオフの場合のリーク電流を増やしてしまっていた。これに対して、Tri-Gateトランジスタではゲートに囲まれた部分のシリコン基板は薄いので、空乏層だけになってしまい下側のシリコン基板の電位の影響が殆ど無くなる。

IBMやAMDが使用しているSOIプロセスでシリコン層を非常に薄くすればシリコン基板が完全に空乏化するFD(Fully Depleted)-SOIとなるが、非常に薄いシリコン層を必要とするため、製造コストが10%程度高くなってしまう。これに対してIntelのTri-gateプロセスによる製造コストのアップは2~3%と小さいという。

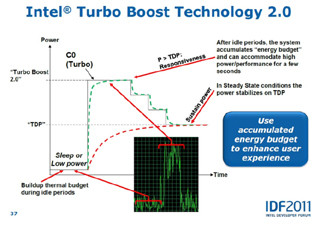

このように、シリコン基板の厚みを薄くしたことでサブスレッショルドスロープと呼ぶ、ゲート電圧がスレッショルド電圧より低い領域でのドレイン電流の傾きが大きくなり、図4のような特性となる。黒線で書かれたカーブがプレナートランジスタのもので、これに対してTri-gateトランジスタではスレッショルド電圧をプレナートランジスタと同じにした場合は、ゲート電圧が0Vのオフ状態でのドレインリーク電流が1/10に減少している。また、同じリーク電流とした場合はスレッショルド電圧を下げることができる。

MOSトランジスタの飽和ドレイン電流は、古典的な式によれば、(Vg-Vt)2に比例する。従って、スレッショルド電圧Vtが下がるとドレイン電流が増えスイッチ速度が高速になる。また、スイッチ速度を一定とすれば、その分、小さなトランジスタで済み、消費電力を減らせる。

電源電圧に対する遅延時間を比較したのが次の図5である。一番上の黒線が現在のSandy Bridgeなどに使われている32nmプレナートランジスタで、キャプションのない灰色の線が22nmプレナートランジスタ、一番下の青線が今回の22nm Tri-gateトランジスタの特性である。

この図にみられるように、22nmのTri-gateトランジスタは、電源電圧1.0Vでは現在の32nmプレナートランジスタと比べて18%高速であり、電源電圧を0.7~0.8Vにしても同程度の性能を持っている。そして、電源電圧を下げた場合には微細化によるゲート容量の減少も含めると、半分以下の消費電力で同等の性能を出せるという。

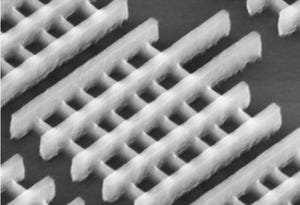

図6に示すトライゲートトランジスタの電子顕微鏡写真の中央の構造は、6本のシリコンフィンと2本のゲート電極を持つ構造であると考えられる。

右下がりの楕円で囲んだものが1本のシリコンフィンであり、それと直行する楕円で囲んだものがゲート電極である。そしてゲート電極と並行してゲート電極の両側にあるものはソースとドレインのコンタクトであると考えられる。ここでは、便宜上、中央の電極をドレインコンタクト、両端の電極をソースコンタクトと書いたが、これは使い方による。また、一方のゲート電極側がPMOS、他方がNMOSとなっているのではないかと思われるが、どちらか一方のタイプのトランジスタであるのかも知れない。

Tri-gateトランジスタは、その物理構造の違いから製造プロセスに与える影響が大きいのは当然であるが、実は設計にも大きな影響がある。シリコンフィンとゲート電極のそれぞれの交点の部分にトランジスタが構成されるが、このトランジスタのチャネル幅はOxideの上に出ているシリコンフィンの高さの2倍+厚みである。なお、チャネル長がゲート電極の幅で決まっているのはプレナートランジスタと同じである。

そして、図6の写真の構造ではこの単位トランジスタが6個並列に接続されている。プレナートランジスタの場合は、原理的には任意のチャネル幅のトランジスタを作ることができたが、Tri-gateトランジスタの場合は、各交点にできる基本単位のトランジスタの整数倍のチャネル幅のトランジスタしか使用できない。

また、このように微細なトランジスタを複数個並列接続して使うことになるので、プレナー型とはシリコン上のトランジスタのレイアウトも異なってくる。このため、回路設計や配置設計などのCADシステムをTri-gateトランジスタ対応に変え、一部では設計するエンジニアの意識も変える必要があると思われる。このため、今回のTick(マイクロアーキテクチャは前世代と同じでプロセスを変更するステップ)は従来のTickよりも大変であったと思われる。

プロセス技術の開発という点では、台湾のTSMCなどもFinFETの論文を多く発表しており、このような3次元トランジスタを開発しているのはIntelだけではないが、設計環境を含めて整備し、実用化にいち早くこぎつけたという点で、やはり、Intelの開発力は卓越していると言える。

Intelはこの製造プロセスを2011年末から2012年早々に発売されるとみられるIvy Bridgeプロセサの製造に使用し、性能とエネルギー効率を改善する計画である。

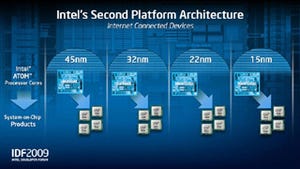

また、Atomベースの組み込みプロセサは、現在は45nmから32nmプロセスへの移行が始まったところであるが、これも順次、22nmのTri-gateプロセスへの移行を予定している。この分野は電池寿命の点から消費電力が非常に重要視される分野であり、Tri-gateトランジスタで電源電圧を下げ、消費電力を半減させることになれば、ARM陣営との対抗で有利な地位を占めることができると思われる。