東芝は4月20日、携帯端末向けにIEEE802.11a/b/g/n準拠の無線LAN対応LSIの低消費電力化技術を開発したことを発表した。

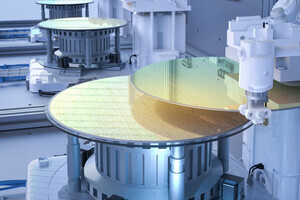

今回試作したチップでは、90nm CMOSプロセスを用いて待機時に動作する回路を最小限にし、常時電源が供給される電源制御回路に厚膜トランジスタを採用することなどにより、待機時の消費電力を7μWまで引き下げることに成功した。

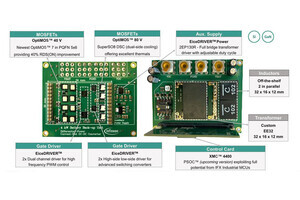

また、同チップには、携帯機器に搭載された場合の使い方を考慮し、通信時の「通常モード」、受信待ち受け時の「スリープモード」、待機時の「ディープスリープモード」の3つの動作モードを用意。それぞれに対応する低消費電力技術を搭載し、通常モード時の動作電力の削減には、 1.0V動作する低電圧セルと、独自の低消費電力フリップフロップ回路を採用したほか、スリープモード時は、チップ内部を複数のブロックに分割してそれぞれの電源をオン・オフ制御するとともに、動作周波数を切り替えることで、消費電力を削減。そしてディープスリープモード時は、スリープモード時と同じ電源、周波数制御に加え、常時オンとなる電源制御回路に厚膜トランジスタを使用してリーク電流を低減した。

これらの技術の導入することで、各動作モードでの消費電力削減を実現しており、特に「ディープスリープモード」時においては消費電力7μWを実現したという。

また、IEEE802.11n SISO(Single Input Single Output)準拠の高速通信を実現することで通信時間を短縮し、消費電力の少ない待機時間を伸ばすことで、動作時の平均消費電力の削減も可能になるとしており、これらの低消費電力技術および高速化技術を組み合わせることで、従来製品比で9割以上の消費電力削減を実現できたとしている。

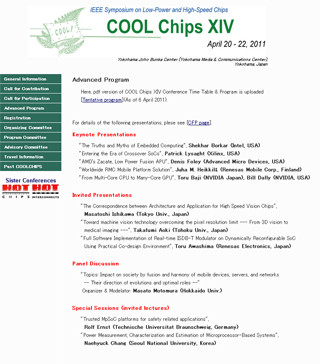

なお、同成果は、横浜で4月20日より開催されている低消費電力半導体に関する国際学会「COOL Chips XIV」において4月22日に発表される予定。