CEVAは、同社の「CEVA-TeakLite-III」DSPアーキテクチャの新製品「CEVA-TL3211」を発表した。

同製品は、CEVA-TeakLite-IIIアーキテクチャに準拠し、コード互換性を確保しており、2G/3Gモデムのベースバンド処理に対応するとともに、次世代デジタルTVおよびSTB設計向けのDolby MS10、並びにMS11マルチストリーム・コーデック、および、すべてのDTS-HDオーディオ・コーデックが認証済みとなっている32ビットオーディオDSP。

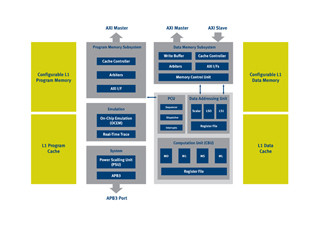

動作周波数は1GHzで、40nmプロセスおよび全二重AXIバスの採用による、低消費電力、より高い性能、ならびに容易なSoCへの統合が可能となっており、実装時のチップ面積を0.2mm2に抑えることが可能だ。デジタルTVおよびSTBでは、200MHz未満ですべてのユースケースが稼働できるため、同一コアを利用して様々なポストプロセッシング機能を走らせるための余裕を開発者に提供することも可能となっている。

また、迅速なアルゴリズム開発および、現実のシステムDDRメモリの制約使用のサポートを可能にし、最終製品の低コスト化が可能となるL2キャッシュ・サポートを含む、キャッシュ・デザイン(プログラムおよびデータ)を採用しているほか、自社の電力スケーリング・ユニット(PSU)サポーティング・クロックおよび電圧スケーリングにより、電力消費の削減、熱放散の低下、および安価なICパッケージの利用を可能にしている。

また、同社は併せて「Dolby HDオーディオ・コーデック・パッケージ」を発表している。同パッケージには、CEVA-TeakLite-III DSPコア向けの7.1チャネルDolby TrueHD、Dolby Digital Plus、Dolby Pro Logic IIx、並びにDolby Digitalエンコーダが含まれている。

CEVA-TeakLite-IIIの上に開発された同パッケージは、ホームエンターテイメントおよびコンシューマIC向けに統合されたHDオーディオで、Blu-ray Discプレーヤ、デジタルTVおよびSTB向けのチップなどに展開されており、要求の厳しいBlu-ray Discのユース・ケースを単一のDSPコアでサポートしており、結果、複数コアのオーディオ・プロセッサを必要とする他のソリューションに比べ、SoC設計を単純化し、全体のコストを抑え、チップサイズの削減を実現することが可能となる。

なお、同パッケージは、CEVA-TeakLite-III DSPコアを基礎としており、コンフィギュレーション可能なキャッシュ・メモリ・サブ システム、HDオーディオ・コーデック一式、ならびにソフトウェア開発ツール、プロトタイプ・ボード、テスト・チップ、システム・ドライバ、およびRTOSを含む、ソフトウェア開発キットを備えている。