Taiwan Semiconductor Manufacturing(TSMC)は4月14日(米国時間)、米国で開催した「TSMC 2010 Technology Symposium」において、22nmプロセスをスキップし、20nmプロセスへ直接移行する計画を表明した。

2012年後半にも20nmプロセスによるリスク量産を計画しており、同社ではこの決定の背景に同プロセスに要求されるパターニング技術とレイアウト設計手法に対する技術的な裏づけがあると説明している。

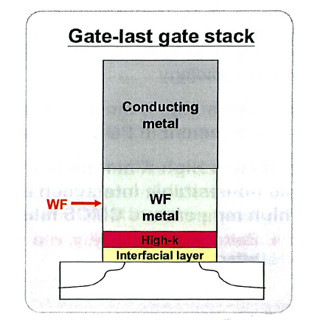

同社が用いる20nmプロセス技術の概要は、プレーナタイプのプロセスを基本に、改良されたhigh-k/メタルゲート(HKMG)、次世代の歪みSi技術、低抵抗Cu配線技術ならびにUltra low-kの配線絶縁膜が採用される計画となっている。また、同社R&D担当上席副社長のShang-Yi Chiang氏によると、FinFETや高移動度素子など、プレーナタイプ以外のトランジスタ構造においても、高い実現可能性を実証したこととしている。

なお、同氏は「「20nmへの移行は22nmプロセス技術と比べて、より高いゲート密度とチップ性能/コスト比を実現し、先端技術の設計者へ、より魅力的なプラットフォームを提供する」としながらも、「TSMCは先端技術開発において、そのROIを真剣に考慮しなければいけないところにきており、今後は各ノード固有のプロセス技術の弊害だけでなく、それを越えた幅広い視点を持つことも必要となってきている。これらの技術的・経済的課題に立ち向かうためには、共同研究あるいは、相互最適化といった新機軸となる考え方が不可欠となる」と今後の技術開発に対する姿勢を表している。