次世代スパコンの技術

理研の開発ディレクタである横川氏は、計算シミュレーションで科学技術、産業の競争力を高め、かつ、スパコン開発力を国内に保持するというのが開発当初の方針で、LINPACK性能10PFlops、実アプリ性能を重視した設計を目指したと述べた。そして、次世代スパコンの技術開発のポイントとしては、10万プロセサ規模の超並列システム、高密度、低消費電力の45nmプロセスによる半導体製造技術、そして、10万プロセサと大規模ファイルシステムと超並列システムを利用するアプリケーションの開発を挙げた。

そして、OSとしてはLinuxをベースとしたOSを使うことを明らかにした。また、10万規模のプロセサからアクセスする共通の高性能ファイルシステムを作ることはほぼ不可能であり、システム全体のデータを記憶するグローバルなファイルシステムと各計算ノードにローカルなファイルを置く構成を取っている。実行に当たっては、最初にグローバルファイルからローカルファイルにデータ転送し、各計算ノードはローカルファイルを使って処理を行い結果もローカルファイルに書き出す、そして処理が終わった時点でローカルファイルからグローバルファイルに書き戻すというように処理が行われる。処理形態としてはバッチで、ジョブスクリプトでグローバルとローカルのファイル間の転送を指示するという。

次世代スパコンのCPUと計算ノード

ハードウェアに関しては富士通の井上氏が説明を行った。中心となるSPARC64 VIIIfxは45nmプロセスで製造される8コアプロセサであり、SIMD拡張を含めてピーク128GFlopsの演算性能を持つプロセサである。

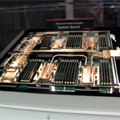

このCPU 1チップとトーラスネットワーク用LSI 1個のペアが計算ノードを構成し、4計算ノードが1枚のシステムボードに収容されている。写真に見られるように、これらのLSIは水冷である。そして、筺体の上下に各12枚のシステボードが収容できるようになっている。なお、中央の部分は電源とI/Oノードである。

SPARC64 VIIIfxプロセサに関してはすでにHotChipsなどで発表されているが、チップ内の8コアの同期をとるハードウェアバリア機構と、HPC-ACEと呼ぶ、浮動小数点演算SIMD機構、レジスタ数の拡大、セクタキャッシュなどのHPC向きの機能拡張が実装されているのが特徴である。

SIMD機構は、IntelのSSEと類似の1命令で複数の演算を行う機能で、1サイクルあたり4個の倍精度浮動小数点の積和演算を実行することができる。SPARC64 VIIIfxのクロックは2GHzであり、2演算(積と和)×4×8コア×2GHzで、チップあたり128GFlopsの性能を実現している。また、標準のSPARC V9アーキテクチャでは浮動小数点レジスタは32個であるが、これでは不足で、レジスタをメモリに追い出し、また、必要になった時点でメモリからレジスタに読み込むという処理が必要となり性能が出ない。これを256レジスタと一挙に8倍に拡張した。富士通の調査では128レジスタあれば66%、256レジスタあれば89%のケースでレジスタ不足は起きないという。

プロセサのキャッシュはハードウェアが勝手にデータの入れ替えを行うので、頻繁に使用するデータでも、新しいデータを入れる場所を作るために追い出されてしまい、再度、メモリからの読み込みを必要としてしまうことがあり、性能を落としている。このため、CELLプロセサではハードウェアが勝手に入れ替えないローカルメモリを使っている。しかし、そのためCELLでは入れ替えを行う部分を明示的に書く必要があり、プログラムの作成が面倒になっている。これに対する富士通の解がセクタキャッシュである。

セクタキャッシュはデータキャッシュを2つのキャッシュに分割して使用する。分割の単位はキャッシュのWay単位で指定することができる。そして、メモリ上のデータを読み込む場合に、どちらのキャッシュ部分を使うかを指定できるという機構である。頻繁に使用するデータを0側、一過性のデータは1側のキャッシュを使うことにすれば、一過性のデータの読み込みで使用頻度の高い0側のデータが追い出されてしまうことは無い。したがって、ローカルメモリと同様の効果が得られる。一方、キャッシュ内のデータの入れ替えについてはハードウェアが自動的に行ってくれるので、ローカルメモリのようなプログラミングの煩雑さがないという。

SPARC64 VIIIfxは電力を大幅削減

SPARC64 VIIIfxはチップ当たりのFlops値ではIBMのPOWER7には後塵を拝するものの、消費電力は58Wと小さく、Flops/WではPOWER7を超える超並列スパコンに適したプロセサである。ただし、この消費電力は水冷でチップ温度を30℃に下げたことによるリーク電力の低減が大きく貢献している。

上記のスライドの右上の図の縦軸は消費電力で20W刻み、横軸はチップの温度で20℃刻みであり、それぞれの点がCPUチップ1個の測定に対応している。温度が上がると消費電力が急増することが良く分かる。また、右下の図は横軸が年度で、各社のCPUチップの消費電力をプロットしており、赤線が富士通のSPARC64 CPUである。前世代のSPARC64 VIIでは130W程度の消費電力であるが、今回は消費電力が少ないトランジスタを使い、無駄な回路動作を抑制し、レジスタ拡張やセクタキャッシュなどのHPC-ACEアーキテクチャによりメモリアクセスを削減してメモリアクセスによるエネルギー消費を減らすなどの工夫で消費電力を58Wまで削減している。

6次元メッシュトーラスによる接続

そして、計算ノード間を接続する6次元メッシュトーラス構造のTofuと呼ぶインタコネクトを新規開発している。ただし、ユーザから見えるのは3次元トーラスで、余剰の次元の接続を使って、システムを分割しても切り口同士を繋いで各部を3次元トーラス構造にすることができるようになっている。また、余剰次元は故障ノードができてもそれを迂回して3次元トーラス構造を維持するためにも使われている。なお、Tofuの各リンクの通信速度は5GB/s×2となっている。

トーラスであるのでクロスバよりもケーブルは少ないと考えられるが、それでもシステムが巨大なので、ケーブル総数は約20万本、総延長は1200kmにのぼるとのことである。これだけのケーブルを床下に収容するため、次世代スパコンを設置するフロアは床を150cm持ち上げた構造になっている。