Fermiアーキテクチャ

では、Fermiアーキテクチャを詳細に見て行こう。

まず、演算を行うコアは、従来はStream Processorと呼ばれていたが、今回はCUDA Coreという名称に変更されている。このCUDAコアはGT200では240個であったが、Fermiでは512個と2.13倍に増強されている。また、これにより使用トランジスタ数も14億個から30億個とほぼ同じ比率で増加している。

チップの全体イメージであるが、中央に768KBのL2キャッシュがあり、その上下に8個ずつのStreaming Multiprocessor(SM)があり、それぞれのSMに32個のCUDAコアがある。そして左右の辺にDRAMインタフェースとホストインタフェースとGigaThreadと書かれたインタフェースが搭載されているという図になっている。しかし、発表スライドのチップ写真を見ると、実際のチップはこの図とは多少、異なっている。

16個のSMは4個×2行でチップの上下に配置され、中央の3個のブロックが同じ配置であるので、それぞれがGDDR5メモリを2チャネルずつ分担しているメモリコントローラであると考えられる。そしてイメージ図では中央にL2キャッシュが描かれているが、チップ写真ではこれは判然とせず、256KBずつ3つのメモリコントローラに分散されている可能性もあると思われる。

FermiのStreaming Multiprocessor

そして、それぞれのSMは、次の図のような構造となっており、16個のCUDAコアが2グループ、16個のロードストアユニット、そして4個のSpecial Function Unitを含んでいる。さらに、SMは64KBのメモリを持ち、このメモリは16KB、あるいは48KBを1次キャッシュとして使い、残りをローカルのシェアードメモリとして使うことが出来るようになっている。

従来のGPUでも16KBのシェアードメモリを持っていたが、Fermiでは汎用CPUと同じようにキャッシュが設けられた点が目新しい。シェアードメモリは、そこに何を入れるかをプログラムで記述する必要があるが、キャッシュの場合はプロセサが適当に使用頻度の高いデータを入れてくれるので、プログラムを作ると言う点では、楽に、そこそこの性能が出せるという点が大きなメリットである。

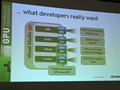

そして、SMはWarp SchedulerとDispatchユニットを2組備えており、2つの命令列(Kernel)を並列に処理することが出来るようになっている。従来のGPUのSMは1時には1つのKernelしか実行できなかったが、Fermiでは16個のCUDAコア単位で別々の命令を処理することができる。また、GT200ではチップ全体で1つのプログラムしか実行できなかったが、Fermiではチップを分割して最大16の異なるプログラムを並列に実行できるようになっている。

ピクセル処理のように膨大な並列度がある処理では大きな問題ではないが、科学技術計算では並列度がそれほど高くない計算もあり、その場合は512個のCUDAコアを一まとめにして使うと余るコアが多くなり、効率が悪いが、最大16分割できると、無駄を減らすことができる。

そして、各CUDAコアは整数演算と浮動小数点演算の実行パイプラインを持ち、浮動小数点演算パイプラインは、1サイクルに1個の単精度浮動小数点積和演算(FMA:Fused Multiply Add)、あるいは2サイクルに1個の倍精度FMAを実行できる。

通常の積和演算ではA×Bを計算すると、その結果TをA、Bと同じビット数に丸めてしまい、それにCを加えるという処理を行うが、Fused積和の場合は、中間結果Tは2倍のビット長でそのまま保持してCを加えるので、計算精度が高いというメリットがある。

また、Fermiの浮動小数点演算器はIEEE754-2008に完全に準拠しているという。GT200のコアの単精度浮動小数点演算器は丸めの処理などを多少サボっており、1~2ビット精度が落ちると言われていたが、これが無くなり、IEEE754で規定されているすべての丸めモードにも対応しているという。

さらに特筆すべきは、通常フォーマットで表現できる最小数以下のSubnormal数の処理をハードウェアで行っている点である。Subnormal数の処理は、汎用CPUでも検出機能だけをハード化し、検出されるとトラップを上げてソフトウェアで処理するというプロセサが多いが、ソフトウェア処理だと、当然、処理速度が大幅に低下してしまう。これをハードを奢って処理しているのは大したものである。

チップあたりの単精度浮動小数点演算能力はGT200では毎サイクル240回の積和(Multiply Add)演算であったが、Fermiでは512積和(Fused Multiply Add)演算とコア数に比例して性能が向上している。一方、科学技術計算で重要な倍精度浮動小数演算はGT200では30FMAであったものが、Fermiでは256FMAとなり8.53倍と大幅に性能を向上させている。

CUDAコアのクロック周波数は公表されていないが、前世代のGPUからみて、1.5GHz程度は実現できると思われる。仮に1.5GHzとすると、単精度のピーク性能は1.536TFLOPS、倍精度のピーク性能は0.768GFLOPSとなる。

AMDのハイエンドGPUである「Radeon HD5870」は単精度ピーク演算性能は2.72TFLOPSであり、これと較べると1.536TFLOPSはかなり見劣りする値である。しかし、最初に掲げた比較表を見ると、GT200の単精度の演算は240FMAと書かれているのであるが、実は各SPはMADD演算器1個とFMUL演算器1個を持ち3演算を実行できる。この比較表では単精度の性能として書かれていないが、GT200と同様に、FermiのCUDAコアにもFMULがあるとすれば、単精度のピーク性能は2.3TFLOPSとなり、HD5870には及ばないものの、まあ、対抗できるレベルの数字になる。