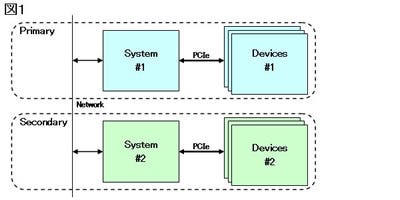

例えば図1の様な構成があるとする。ものは何でもいいが、例えば決済システムの様に、ダウンが許されないクリティカルなシステムだ。こうしたものでは、複数の構成を用意し、片方がダウンしたらもう片方でカバーするといった形の運用でシステムダウンを避けようとする。図1の例だと、普段はSystem #1の方を使うが、System #2も常に通電状態においておき、System #1に問題があったら直ちにSystem #2に処理を移すというものだ。

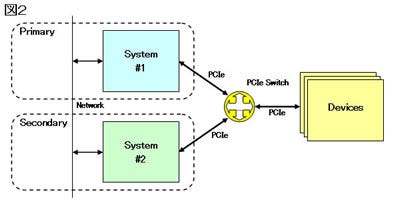

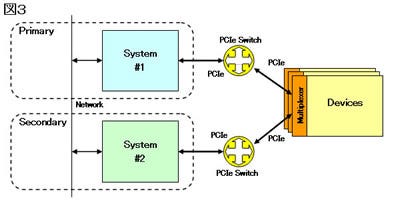

ただ図1の例ではDeviceを別に持つことが出来たが、実際には例えば決済データベースを複数持ってもデータの同期が大変だし、物理的にも複数台置けない場合がある。データベースはデータベースで内部的に冗長性を持たしているから、ここで更に冗長性を取る事に余り意味は無い。そこで、本来は図2の様な構成をぱっと取れれば効率的なのだが、実はこうした仕組みはPCIeではサポートされていない。どうしてもこれがやりたい場合、図3の様に各PCIeデバイスにPort Multiplexerを付けて繋ぐという、やたら滅多ら高価な構成が必要になった。ただこれはあまりに不便ということで、PCI-SIGもMR-IOV(Multi-Route I/O Virtualization)を標準化し、図2の様な構成を可能にした。ところがMR-IOVの場合、PCIe Switchと各Deviceが全てMR-IOVに対応していないと使えないため、結局のところ高価な構成であることに変わりはなかった。

こうした問題に対しての解決策として各PCIe Switchベンダーが提供してきたのが、Non-Transparent Bridge機能付きSwitchである。要するに図2/3における根本的な問題は、PCIe Deviceは基本的に1つのHostしかサポートしない/出来ないという話で、Port ReplicatiorはDeviceに対して複数のHostを1つのHostに見せかける機能を持つし、MR-IOVはDeviceに複数のHostをサポートさせるための拡張である。Non-Transparent BridgeはPort Replicatorを進化させたもので、要するにSwitchを高機能化させ、複数のHostからの要求を1つのHostからに見せかける機能を持つ。価格的にはおもいっきり高価だが、各DeviceにPort Replicatiorを装着するよりもトータルでは安価になる。

この機能をJasper Forestは内蔵しているから、より安価に冗長性を確保したシステムが構築できるということになる。また2つのシステムをPCIe Backplane経由でDual Processorとして動作させられるというあたり、相当PCIeの内部に手を入れてある感じだ。なるほど、LynnfieldやJasper Forestで妙にPCIeのコントローラが大きな面積を占めている訳である。

このSolutionが微妙なのは、そもそもNon-Transparent Bridgeの仕組みがPCI-SIGで標準化されていないことだ。Non-Transparent Bridge機能搭載PCIe Bridgeは複数のベンダーから出荷されているが、これらは各社独自のインプリメントを行っており、互換性が無い。Intelもまた当然独自に拡張を行ったと思われるが、PCI-SIGでPCIeの標準化を率先して行っていたIntelが、こうした独自拡張を行うのはちょっと解せない部分である。というのは、例えばGeneseoにしても(多少強引なところはあったにせよ)ちゃんとPCI Express ExtentionとしてECNをリリースし、最終的にPCI Express Version 2.1としてSpecificationに取り込むという手続きをとっているだけに、なぜこれを勝手に出したのかが非常に興味深いところである。