システムLSIに適したMRAM構造

一方、NECエレクトロニクスとNECが共同で開発を行ったMRAMは、「他社が行っているMRAMとの違いは、3端子のデバイスとしたところ」(NECデバイスプラットフォーム研究所 所長の望月康則氏)で、「システムLSIの混載に向けた、"本気"のメモリセルができた」(同)とする。

読み出し方式は従来のMRAMと同じながら、書き込み方式としては、「スピントルク磁壁移動方式」を採用。シミュレーションによる予測では、従来の磁場書き込み方式がプロセスの微細化に伴い書き込み電流が増大していたのに比べ、スピントルク書き込み方式では、低減できるとされていた。

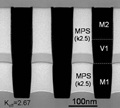

実際に4kビットのメモリセルアレイを9つ並べた実験用チップを試作。アレイの構成はCMOSプロセスの上にMRAMプロセスを載せるというもので、100nmプロセス以下で目標としていた書き込み電流0.2mAを達成できる見通しが確認されたという。

今回のMRAMの構成を簡単に説明すると、MOSトランジスタのような形をイメージしてもらえると分かりやすいと思うが、MOSトランジスタのソース/ドレイン部分に相当する部分に安定した強力な逆方向に向いた磁石を配置、ゲート部分は絶縁膜の上に同様に磁石を配置、MOSトランジスタと異なるのは絶縁膜とソース/ドレインの間に強磁性体自由層が挿入される点といった形となる2T1MTJ。

NECでは、2007年6月に強磁性体自由層の磁壁移動方式を提案していたが、その時は面内磁壁の利用であった。今回は、これを垂直磁壁を利用する方法に切り替えた。ちなみに、自由層そのものは同じ方向に向きたがる小磁石の集団であり、安定した2つの下部の磁石のを活用することで磁石の向きをソース相当側とドレイン相当側で逆にすると、その境界面で磁石の向きがまったく違う方向に領域が形成されるが、その領域が磁壁と呼ばれている。

垂直磁化膜とするために、同社では磁壁を電流のスピントルクで移動させ、磁壁の位置が"0"と"1"となるようにMTJ(Magnetic Tunneling Junction)を形成したほか、磁石が垂直方向に向くように自由層の材料をNiFeからスピン分極率の高いCoNiの多層膜に変えるなど、構造、材料の最適化を行っている。

電流と電子は逆方向に流れるが、伝導電子も微小磁石の性質を持っており、強磁性自由層の小磁石と相互作用が生じることで、磁石の方向を揃えるように作用するのがスピントルクな訳であるが、この作用により書き込み電流を流すと、電子の流れに沿うように磁壁は電流の方向とは逆方向に移動することとなる。ただし、安定した磁石の上部の自由層も磁石の向きは常に安定しているため、その手前で磁壁は止まることとなる。結果として、そこで磁石の方向が上向きか下向きか分かれることとなり、"0"か"1"が規定されることとなる。

実際に試作した回路は、150nmプロセスを採用。2T1MTJで構成されるため、書き込み線がセルごとに分離、書き込み時の他セルへの御書き込みが発生しないため設計が容易にできる。また、実際の実証実験では、磁壁の移動速度は50m/sとなり、100nmで2ns(=500MHz相当)となるとしており、素子の縮小によりさらに高速化が可能になるとしている。このため、システムLSI内へ組み込む場合、内蔵SRAMの代替のほか、外部フラッシュメモリの代替に加え、論理回路を不揮発性レジスタとし、そこにMRAMのプロセスを導入することで、論理回路の不揮発化もできるようになるという。「システムLSIのすべての回路をMRAM化することで、待機電力ゼロのシステムLSIが実現可能になる」(NECデバイスプラットフォーム研究所 研究統括マネージャーの笠井直記氏)としており、1ms以下での電源のON/OFFができるようになることから、例えばキーボードの入力直後のみ電源が入るようなシステムの構築が可能となり、これまで以上の低電力化が図れるようになるという。

NECでは、「微細化を進めると、より本来の実力がでてくる構成」(笠井氏)としており、55nm、40nmプロセスといった先端プロセスでの試作を進めたいとしているほか、大容量MRAMをシステムの中に組み込んだ形での動作検証を目指した設計・試作を行っていく計画としている。