Virtex-6とSpartan-6

さて、ここからは同社のCharles Tralka氏(Photo13)に代わって、具体的なVirtex-6とSpartan-6の詳細の話が始まった。

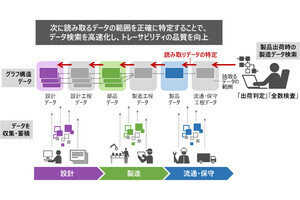

まず最初に、直近でXilinxがターゲットとしているアプリケーション領域が簡単に示された(Photo14)。このターゲットに対して、今回発表されたのはSpartan-6が2製品、Virtex-6が3製品となる(Photo15)。内部構造で言えば、Spartan-6はLXからパラレルI/Oを減らして、その分をPCI Expressに振ったという感じだが、Virtex-6は目的に応じて明確に内部構成を変えているのが判る(Photo16)。もう少し内部構造を見てみると、VirtexとSpartanは、規模こそ違うものの、それを除けば概ね同等の構造とされている(Photo17)。またトランシーバについては、従来のGTP/GTXに加え、新たに11.2GbpsのGTHトランシーバをサポートした(Photo18)。これらによって、広範なI/Fが提供されることになる(Photo19)。

次に消費電力であるが、そもそもプロセスの微細化により低電圧動作が可能になった上、電源電圧オプションが用意されたり、Clock GatingやHard Wiredなど消費電力を下げるオプションがいくつか用意され、これらを駆使することで従来製品に加えて最大65%の削減が可能としている(Photo20)。

開発環境については、先ほどPhoto11でピラミッド構造が示されていたが、もう少し細かく説明がなされた。まず基本プラットフォーム(Photo21)では、基本的なものが提供される。従来Xilinxの場合、リファレンスボードとかIPなども、しばしば用途別にバラバラに提供されてきていたが、Virtex-6/Spartan-6ではこのあたりを共通化し、どんなドメイン/用途向けであっても、リファレンスデザインなどは共通化される事になった。

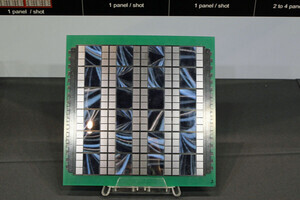

ただそうなると、IPやソフトウェアはともかくハードウェアはどうなる? という話は出てくるが、今回からリファレンスデザインは共通のベースボード+特定用途向けメザニンカードの形で提供されるようにするとの事で(Photo22)、差異はこのメザニンカードで吸収するという事だそうだ。その差異を提供するのは、「ドメイン特化部分」ということになる(Photo23)。

|

|

|

Photo22:これは会場で動作デモを行ったSpartan-6のベースボード。黄色で囲まれた部分は、カメラI/FとDisplay I/Fを搭載したメザニンカードとなる |

Photo23:ここではFPGAを「どういう使い方をするか」で分類する形になる |

その先がマーケット特化部分ということになり、このあたりまでは標準ソリューションが提供される形だ(Photo24)。最後が顧客固有のデザイン(Photo25)ということで、市場特化部分までうまくIPやツール、ソフトウェアを入手できればクライアントはこの部分だけに開発を集中すれば良い事になる。これらの提供時期だが、2009年第2四半期から提供が始まり、特定市場向けに関しては2010年あたりから本格投入になる模様だ(Photo26)。

さて、ここからは具体的な利用例が幾つか示された。まず車載Infortainment Systemである。従来はSpartan-3に外付のImage Processorで構成されていた製品(Photo27)を、Spartan-6に置き換えたところ、Image ProcessorをSpartan-6に取り込むことに成功したという(Photo28)。この結果、EBOMを83ドルから41ドルに低減し、かつ消費電力も6.5Wから1.4Wに削減が可能になった(Photo29)。

次はFPDのコントローラで、従来は2つのFPGAを含む5チップ構成だった製品(Photo30)をSpartan-6で置き換えた例(Photo31)。消費電力の低減と信頼性向上、システムコスト低減に役立ったとしている。

|

|

|

Photo30:このケースでは発熱が問題だったそうで、コントローラ部の低消費電力化が主要な目的だった模様 |

Photo31:再利用可能なIPというのは、Xilinxが特定市場向けに提供するIP(LED DriverやImage Processing)、ASICで使われていたIP、および顧客が独自に持っていた画像改善回路のIPなどで、それらはすべて再利用されたとのこと |

Virtexの事例では、3GPP-LTEの基地局向けに、従来Virtex-5を2つ使っていた構成(Photo32)を、Virtex-6では1つに集約できた(Photo33)とか、光ルータ(Photo34)でASICやMUXを置き換える事で7チップから4チップに集約した(Photo35)例、あるいはその他の用途に向けた実例が示された(Photo36)。