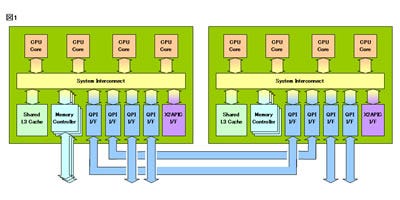

では仮に45nm世代で8coreを作る場合どうなるか? というと、筆者は図1の様な構造になると想像している。つまりQuad Coreのダイを2つ並べ、間を2本のQPIで接続するという形態だ。こうすれば、パッケージ全体として外部に出るQPIは4本となるし、2つのダイの間は高速に接続されるから、帯域あるいはレイテンシの問題も少ないだろう。ただ問題なのはMemory Controller。図1では、片方のCPUのみにMemoryが接続される形態を示したが、ひょっとするとこれは両方のCPUダイにMemoryが接続される可能性もありうる。ただそうした場合、明らかにパッケージのピン配置がQuad Core製品と異なってしまう。大体、いくらなんでも1つのCPUパッケージから6chものDDR3 Memory Busが出るのは異常であり、精々が各CPUダイともに2chづつに減らされ、合計で4本というあたりではないかと思う。

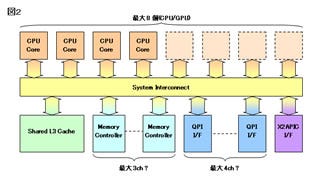

ついでに、Nehalemの内部構造を図2にまとめてみた。ポイントとしては、

- CPU/GPUはNehalem世代から、恐らく最大8個まで対応している。Photo02に出てくる「最大8coreのscalability"がこれを示唆している。ただし、実際の45nmのNehalem世代では、最大4coreに留まるだろう。

- L3 CacheやMemory ControllerはSystem Interconnect下に位置する形になる。System Interconnectは恐らくSwitched Fablicで構成されるだろう。

- Memory Controllerは、各々が64bit/72bit幅で独立に動作することになる。これまでは2chのMemory I/Fが同期して128/144bitとして動作するのが一般的だったが、Nehalem世代ではAMDのBarcelona同様に、別々に動作することになると思われる。

というあたりだろう。

まず1つ目だが、これは既に述べた通り、ダイサイズの制約からNehalem世代で8coreは非現実的である。ただ、Interconnectに関してはいまのうちから8coreの対応を作りこんでおいても害はない。この状態で動作を検証しておけば、Westmere世代でスムーズに8coreに移行できる。こうした事はこれまでもあった。たとえばIntelはWillamette世代からHyper-Threadingをインプリメントしてあったし、AMDはK8で最初からSRQをDual Core対応としてインプリメントしていた。今回も、あらかじめ8core分をインプリメントしていると考えるほうが自然であろう。

2つ目だが、Memory Channelの数が構成によって変化するという時点で、Memory ControllerがCPU CoreやL3 Cacheからある程度独立していないと構成が面倒になるということは容易に想像できる。

最後に3つ目だが、3chという構成がある時点で、全てのMemory Controllerが同期して動くという事は考えにくい。各々が非同期の場合のメリットはもう一つある。2009年にはGPUを統合したNehalemが登場する予定だが、こうした場合にGPUのフレームバッファが置かれるメモリバンクは画面リフレッシュのために定期的にアクセスされる。こうしたケースでは、CPUからのメモリアクセスと分離してアクセス出来る方が確実である。

といったあたりだろうか。