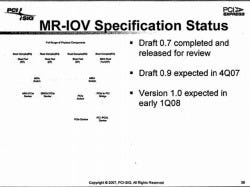

最後がVirtualizationである。既にATS(Address Translation Services)がリリースされているが、これに加えてSR-IOV(Single Root I/O Virtualization)もリリースされた(Photo15)。ここまでは予定通りであるが、案の定MR-IOV(Multi Root I/O Virtualization)はやや遅れることになった(Photo16)。元々の予定(Photo17)では既にDraft 0.9がリリースされ、今年中に1.0が出る予定だったから、1四半期ほどの遅れである。これに関してはYanes氏もタッチしていないようで、詳細は良くわからないということだが、Draft 0.5→0.7ではかなり紛糾があったようで、結局0.7をまとめるのに第3四半期を使い切ってしまったようだ。ただRamin Neshati氏(PCI-SIG Board of Directors。別の肩書きはManager, I/O Standards and Enabling, DEG Architecture and Planning, Intel)によれば、通常Draft 0.7になるとかなりStableなので、その先で大きく変わることはあまりないそうで、これを信じれば来年早々にも1.0がリリースされる事になる。

|

|

|

Photo15:プレゼンテーションでは「来週公開予定」になっているが、これは9月の話であって、既にVersion 1.0が公開されている。 |

Photo16:印刷がかすれて左側が意味不明になっているが、これはPhoto17と同じものが掲載されているだけ。 |