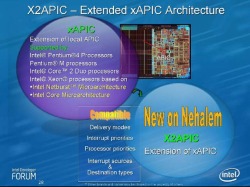

次いでX2APICである。図1/2の右端にも入れてあるのだが、Nehalem世代からX2APICという新しいAPICが採用されることが明らかにされた(Photo04)。このX2APIC、論理的には2^20個、物理的にも40億個のプロセッサをサポートするという、とてつもない拡張である。

|

|

|

Photo04:とりあえず従来のxAPICへの下位互換性は保たれるので、古いOSでも問題なく動作することになる。 |

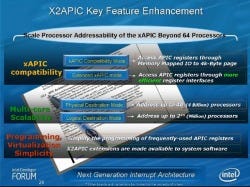

Photo05:X2APICはxAPIC互換モードとExtend xAPICモードの2つを持つ。丁度32bit modeと64bit modeの様なイメージだ。 |

さてこの中で気になるのは、"Access APIC registered through more efficient register intafaces"の項目。要するにAPIC RegisterをI/O空間にMapする訳では無い事がここから想像される。どのみち、2^20個なんて膨大な数のCPUをハンドリングできるようにAPICは作られていない訳で、新規にレジスタ類を作ることになる。これがI/O空間に無い、ということはSpecial Registerとして定義されると考えるのが一番無難である。また、現在のxAPICでは、各CPUのLocal APICとチップセットに置かれたI/O APICが3線式のシリアルバスで接続されているが、プロセッサ数が膨大になると、こんなものでは遅くて使い物にならない。当然こちらももっと高速なものになると考えるべきだろう。こちらもまだ詳細は不明だが、GHzオーダーの転送速度まで引き上げられても不思議ではないように思う。