しかし、何と言っても、Nehalemのウリは、メモリコントローラの内蔵と、高速シリアルバスによるCPUチップ間やI/Oハブとの接続である。これにより、メモリバンド幅が低いとか、メモリレーテンシが長いとか、永らくHyperTransportを使うOpteronに付けられていた差を一気に解消することが出来る。

この高速シリアルバスは、従来、CSI(Common System Interconnect)と呼ばれていたが、今回は、マーケティング用の名前が付けられ、Quick Path Interconnect(QPI)と呼ばれることになった。

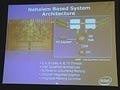

発表された4ソケット構成の図では、CPUチップから4本のQPIが出ており、他の3個のCPUチップに各1本が接続され、残る1本がI/Oハブに接続されている。

Nehalemベースのシステム構成図(出典:Intel) |

この図に見られるように、 2個のNehalemチップがI/Oハブを共用する構成であり、片側のCPUチップが死んでも、他方のCPUからI/Oへのアクセスが可能な構成となっている。そして、メモリはDDR3 DRAMをサポートしており、Bufferedだけでなく、Un-BufferedのDIMMもサポートすると書かれている。今回公表されたNehalemは、3チャネルのDDR3をサポートするチップであるが、DDR3では各チャネルには最大でもDIMMが2枚しか接続できないので、大規模サーバではメモリが不足する。このため、噂では、4+1チャネルのFB-DIMMを接続するバージョンも開発されているという。

また、今回の発表ではQPIの仕様は発表されなかったが、1レーンの転送速度は4.8~6.4Gbpsで、QPIの1チャネルは20レーンで構成されていると言われている。そして、各レーンは1/2レーン、1/4レーンの単位に分割しても使用できると言う。この仕様は、5.2Gbpsで16レーンというAMDのHT3の仕様を若干上回る。

上の図のように、Nehalemは最大8コアまでを搭載するファミリが作られる予定であるが、今回公表されたチップは4コアチップである。このチップの大きさであるが、ウエハの写真から判断すると、おおよそ20mm×13.6mmで、ダイシング(ウエハからチップへの切り出し)のロスを考えると270平方mm程度のチップであると考えられる。公表されたチップ写真では、チップの上辺に40個(あるいは42個)のブロックが並んでおり、この部分が20レーン(あるいは21レーン)×4chのQPIのトランシーバであると考えられる。そして、その下に4個のプロセサコアが並び、一番下の30%程度の領域がキャッシュメモリで占められている。

Nehalemのチップ写真(出典:Intel) |

そして、コアとキャッシュメモリの両側の黒い領域には3チャネルのDDR3インタフェースのドライバ、レシーバが配置されており、コアとキャッシュの中央部にクロスバとDRAMコントローラとおぼしき部分が収容されていると考えられる。