ONFI

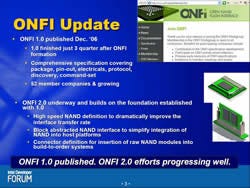

メモリつながりでちょっとFlash Memoryに関する話題をお届けしたい。Intelほか業界各社は昨年、ONFI(Open NAND Flash Interface)と呼ばれる新しい業界標準団体を設立した。ONFIのChairmanは、SATA-IOのChairmanを勤めるKnut Grimsrud氏(Photo24)が兼任する。さてそのONFIとは何か? というと、NAND Flash Memoryの電気的なインタフェースの標準化である。つまりONFIに準拠したデバイスは、やはりONFIに準拠したNAND Flash Memoryならどこのベンダーのものでも利用できることになる(Photo25)。このONFI、発足当時はIntel以外のベンダーにどこが加盟しているのかも明らかにされなかったが、現在は加盟ベンダーの一覧が示されている(Photo26)。ただこれを見れば明らかな通り、ONFIに参加しているのはFlash Memoryを「使う」主要なベンダーと、Flash Memoryを供給する「その他の」サプライヤーのみ。NAND Flashにおける主要なサプライヤーが含まれて居ない、というあたりに、こうした標準I/Fの難しさが見て取れる。

|

|

Photo24:全てのStorage Interconnectに顔を出しているのではないか? という気がするGrimsrud氏。ただGrimsrud氏が出てきた時点で、IntelはNAND Flashを真剣にStorageとして考えている事が判る。 |

|

|

|

Photo25:Quick Summary。現在はあくまで電気的及び機械的互換性を確保したレベル。2.0では高速転送とかNANDモジュールなども追加される。 |

Photo26:これを見ると、Samsung及び東芝という、2大NAND Flashベンダーが含まれて居ない事が判る。もっともONFIのFAQの最後を読むと、Samsungは規格に前向きであるというステートメントはあるが、これはある種常套句なだけに、このまま信じて良いものかどうか。東芝への言及が無いのも気になるところ。 |

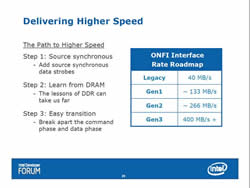

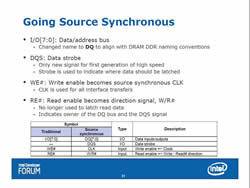

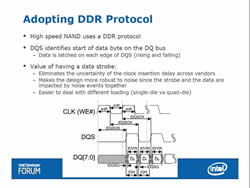

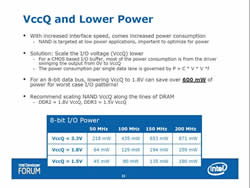

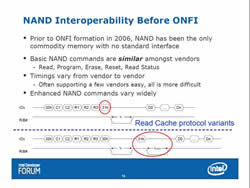

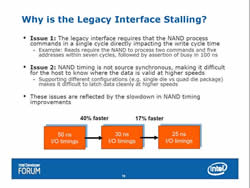

さて、そういう政治的な話は置いておき、ONFIが何を規定したかという話を次に説明する。NAND Flashに関しては今のところ標準的なI/Fというものは無い。勿論、NOR Flashのものをベースにしている関係で大まかな構造は同じであるが、細かくみると互換性が無い(Photo27)。また効率も決して良くはない(Photo28)。そこでONFIではGen1~Gen3という3つの世代を用意し、最高400MB/secに達するI/Fを規定することにした(Photo29)。こうした高速化を実現するために必要な最初の技術はSource Synchronousである(Photo30)。要するにFast Page DRAM→SDRAMへの移行と同じように、送受信の基準Clockを追加し、これに同期する形で送受信を行う形に切り替えるという話だ。更に転送はDDRで行われる形になっている(Photo31)。面白いのはI/O電圧である。既に様々な製品があることを考慮してか、VccQには3.3/1.8/1.5Vが用意される(Photo32)。

|

|

|

Photo27:とりあえずコマンドの拡張は各ベンダーが独自にやっているし、タイミングはベンダー、というよりも下手をすると製品毎にまちまちだったりする。 |

Photo28:バースト転送モードを持たず、また転送タイミングがクロックに同期していないために余分なタイミング調整が必要、という話。バースト転送を追加することで40%高速化出来、更にクロックに同期させることで17%の高速化が可能になると見ている。 |

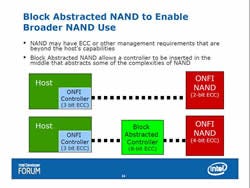

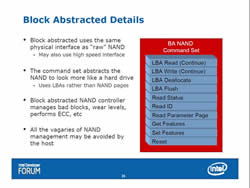

更に、既に様々なNAND Flashがあることを考慮して、BAC(Block Abstracted Controller)を挟むことで互換性を維持する仕組みも用意される(Photo33)。BACは見かけ上、NAND Flashと全く同じI/Fを提供するので、ONFI ControllerはNANDに合わせてパラメータを変えなくても良いということである。殆どのONFI ControllerはASICの形で提供されるから、これを変更するのは大変である。そこでBACで抽象化してしまい、あとはBACの中をいじる方が多様多種のNAND Flashに対応しやすい、ということだろう。

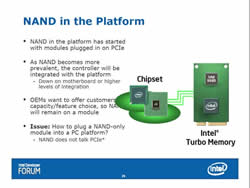

こうしたONFIのメリットはどこに出るか? という代表例が、Intel Turbo Memoryだろう。誤解の無いように書いておけば、現在のIntel Turbo MemoryはONFIには未対応である。これはONFI 1.0のSpecが決まったのはごく最近であり、一方Robsonの開発はずっと前から行われており、急にONFI対応という訳にはいかなかったからという事だそうだ。逆に言えば将来は可能性があるのか? という疑問に対して、「技術的には可能性がある」という、含みのある答えがGrimsrud氏からは返ってきた。これに関しては、例えばOEMがIntelのNAND Flashと互換性のある別のメーカーのFlash Memoryを持ってきてTurbo MemoryのControllerに接続するというSolutionは有りか? とMobile関係者に聞いたところ「OEMが望めばそういうSolutionは可能だろうが、Intelとしてはその動作は保証できない。RobsonのControllerはIntelのFlashのみを対象にValidationをしており、別のメーカーのFlashでの動作は検証していないからだ」という答えが返ってきた。

実のところ、このあたりがONFIの普及の最大の問題となるのではないか、と思う。仮にRobson 2.0がONFIに対応したとする。さて、IntelはONFIに対応した全てのFlash Memoryに対してValidationする必要があるのだろうか? それは幾らなんでも無茶というものだ。従ってIntelはONFI対応のいくつかのNAND Flashを選んでValidationを行い、その結果をもとに「このFlash Memoryは動く」というCommitmentを出すしかない。これを解決するためには、誰かがInteroperability Testを実施するしかない。少なくともJEDECはDRAMに対してInteroperability Testを実施している。同様の作業をONFIが主催しないかぎり、ONFIが普及するのは難しそうに見える。

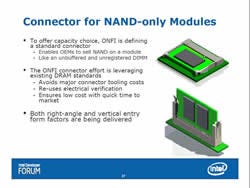

これを助長するのか、それとも助けるのかはわからないが、ONFI 2.0ではモジュールの形での接続に関する標準化も行う、としている(Photo36)。これは機器ベンダーからの要望が高かったそうで、実際Intel Turbo Memoryなどこの形式の方がOEMには好まれそうな気がする。で、これがなぜ助けになるかもと言えば、こうなるとガーバーの標準化は必須だろうし、そうなるとInteroperability Testがやりやすくなるからだ。逆に言えば、Interoperability Testが実施されないかぎりモジュールの普及はないだろうし、このあたりでは具体的にテストスケジュールが出てきそうな気がする。