CPUチップの性能が上がれば、それに比例して多くのデータをメモリから読み、処理結果をメモリに書き込む必要があるが、DRAMチップのメモリバンド幅の増加は、CPUの性能向上に追いついていない。

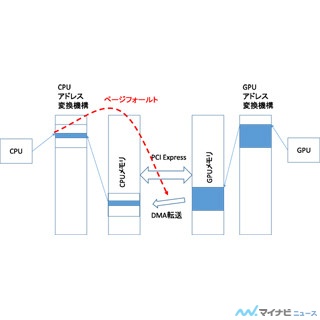

このため、GPUでは、GDDR5などの高バンド幅メモリを使っているが6Gbit/sのような高速伝送を行うため、GPUチップと1対1に接続しかできず、メモリ容量を大きくすることができない。また、 ECCをつけるには36ビット必要であるが、GDDR5は32ビット幅なのでやりにくいという問題もあり、サーバ用には使えない。

このような問題を解決し、高バンド幅で、多数チップを接続してメモリ容量を拡大でき、さらにサーバでの使用に耐える信頼度を持つメモリとしてMicronはHybrid Memory Cube(HMC)を考案し、HMCコンソーシアムを作って開発を進めている。

HMCとはどのようなメモリか

HMCは4枚、あるいは8枚のDRAMチップとロジックチップをTSV(Through Silicon Via)で接続する3D実装のメモリである。

DRAMチップは16区画に区切られており、縦方向の同じ位置の区画のまとまりをVault(金庫)と呼んでいる。つまり1個のHMCには16のVaultがある。このVaultは独立したメモリのように働き、各Vaultがエラーの検出、訂正やリフレッシュを行う単位となっている。このメモリチップのスタックとロジックチップの間にはTSVによる多数の接続があり、1Tbit/s以上のデータ転送バンド幅がある。

ロジックチップはVault対応の16個のメモリコントローラとプロセサなどと接続するリンクインタフェースコントローラと、それらの間を接続するクロスバを持っている。

次の図のように、31mm×31mmと16mm×19.5mmと2種類のパッケージがあり、大きいパッケージは4リンク、小さいパッケージは2リンクとなっている。各リンクは送信、受信ごとに16レーンからなり、各レーンの信号伝送速度は10Gbps、12.5Gbps、そして短距離の場合は15Gbpsの伝送速度となっている。

10Gbpsで、4リンクを並列に使うと、CPUとの間で1.28Tbps(160GB/s)のメモリバンド幅が得られる。DDR3-1666 DIMMのバンド幅が7GB/s弱であるのに比べると圧倒的な高バンド幅である。

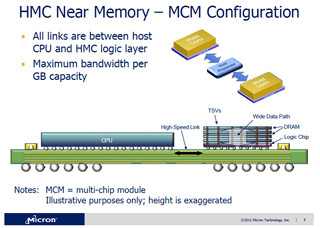

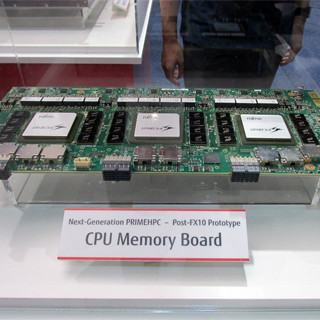

このHMCとCPU(あるいはGPU、FPGA)を直結する構成は、スパコンやサーバ、あるいはGPUのメモリとして最適である。また、ネットワーク機器やテスタなどで、高メモリバンド幅を必要とする構成にも適している。

そして、HMCのリンクは他のHMCを接続することもでき、最大4つのHMCを直列に接続することができる。したがって、次の図のように4個のHMCを直列に繋ぐ形態や1つのHMCをCPUに繋ぎ、そのHMCから3つのHMCを繋ぐというようにして、多くのHMCをCPUに繋ぐことができる。現在、サンプル出荷中のHMCは2GBのメモリ容量であるが、このような接続でプロセサに繋がるメモリの容量を増やすことができる。なお、Micronは、2014年中には4GBのHMCを出すとアナウンスしている。

また、将来的にはリンクの伝送速度を向上させたり、光リンクを使うなどの拡張を考えているという。

HMCは、高メモリバンド幅と直列接続による拡張性だけではなく、高信頼度にも配慮している。

VaultのデータはECCがつけられており、ロジックチップが書き込みの際のチェックビットの生成や、読み出しの際のエラー検出、訂正を行う。また、高速リンクのデータはCRCで保護され、エラーが検出された場合はリトライを行う。そして、ロジックチップとDRAMアレイの間にもチェックが付いている。

そして、通常のDRAMにはほとんどRAS機能が付いていないが、HMCではロジックチップが、チップキルやスクラビングなどの機能を持ち、ミラーリングやロックステップなどの構成もサポートされている。つまり、通常、CPU側で行うRAS機能をすべてHMCがやってくれる。