前世代製品比で性能/電力を2倍に改善

Zynq UltraScale+はTSMCの16FF+プロセスで作られ、FinFETトランジスタは、従来のプレナープロセスのトランジスタと比べると、高速でスイッチし、リーク電流も少ない。

従来の7シリーズは28nmプロセスで作られており、電源電圧は1Vであったが、UltraScale+は標準版は0.85V、低電圧版は0.72Vの電源電圧で動作する。次の図に示すように、28nmの7シリーズと比較すると、標準版は性能は1.6倍に向上し、電力は0.8倍に減少し、性能/電力は2倍に改善する。また、低電圧版は性能は1.2倍であるが、電力は0.5倍となり、性能/電力では2.4倍の改善が得られる。

また、Zynq UltraScale+ではUltraRAMという新しいメモリが提供され、最大432Mbitの容量を持つので、従来は外部メモリとせざるを得なかった大きなバッファを内蔵することができるようになる。

また、大容量メモリのところにはHMCの絵も描かれており、高バンド幅の3D積層メモリを搭載する製品も登場しそうである。

次の図は28nmプロセスを使う7シリーズと20nmプロセスのUltraScale、そして今回の16FF+プロセスのUltraScale+のロジックファブリックの性能/W、高速I/Oのバンド幅、DSPのバンド幅とオンチップのメモリ量を比較したものであるが、28nmの7シリーズと比べるとロジックファブリックの性能/Wは2.4倍、I/Oバンド幅は3倍、DSPバンド幅は4倍に向上している。また、メモリ容量はUltraRAMの採用により8倍に増加している。

FPGAは各種の高速トランシーバが使えるのがその魅力の1つであるが、Zynq-7000では12.5Gb/sのGTトランシーバだけであったが、今回のUltraScale+では32.75Gb/sのGTY、16.3Gb/sのGTHとより高速のトランシーバが追加された。また、プログラマブルシステム側にPCIe、USB、DPなどをサポートするための6Gb/sのGTRトランシーバが追加されている。これらのトランシーバはFPGAロジックを経由することなくプロセサから直接アクセスできるので、使い勝手が良い。

また、1つの発振器のクロックから、9.56GHzのOC-192のクロックと10.31GHzの10Gbase-Rのクロックなどの単純な整数比でないクロックを発生させることができるようになり、複数の発振器を使わなくても済むようになっている。

|

|

32.75Gb/sと16.3Gb/sの高速トランシーバが追加され、プロセサ側からアクセスできる6Gb/sのトランシーバが追加された。また、単純な整数比でないクロックも発生できるようになり、複数の発振器を必要としなくなっている |

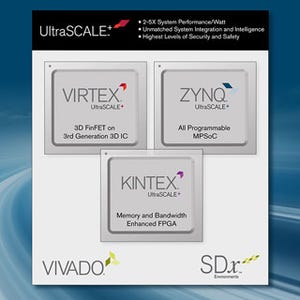

Zynqの第2世代となるZynq UltraScale+は各種の処理に適用できるようになり、「SDSoC」というフルシステムの最適化コンパイラも用意されており、開発が容易になっている。また、プロセサ性能は3倍、メモリバンド幅は4.5倍、FPGA部は性能が60%向上し、性能/Wは2.5倍となっている。

このチップはTSMCの16FF+プロセス用に設計され、2015年6月にテープアウトを行ったという。

(次回は9月15日に掲載します)