MIMDになったCM-5

CM-1からCM-200までは、CPU部に自社開発のLSIを使ったが、VLSIの進歩は目覚ましく、1990年代になると汎用のCPUチップを使う方が機能や性能の点で有利という状況になってきた。また、汎用のプロセサで、ソフトウェアが充実しているアーキテクチャのプロセサであれば、ソフトウェアの開発の手間を大幅に削減することができる。

このような考えから、1991年に発表したCM-5のプロセサとして、TMCはSun MicrosystemsのSuperSPARCプロセサを選択した。そして、1つのCPUチップに4個のWeitekのFPUによるベクタ処理エンジンを接続した。なお、ベクタユニットはオプションであり必須ではなかったが、大部分のユーザはベクタユニットを付けてシミュレーションに使ったようである。

SuperSPARCのCPUクロックは32MHzで、CM-2のCPUの7MHzに比べると4~5倍高速になっている。また、それぞれのSuperSPARCチップが命令のフェッチと実行機能を持つ独立のプロセサであるので、CM-5はMultiple-Instruction-Multiple-DataのMIMDマシンとなった。プログラミングの観点では全てのプロセサが同じプログラムを実行するという使い方が多かったと思われるが、後で述べるように、マシンを分割して、メインの大規模な実行マシン、プログラムデバグ用の小規模マシン、ソースコードの入力などのためのタイムシェアリングマシンに分割して使用するようなこともMIMDであれば自由にできるし、SIMDであれば条件分岐の場合は全プロセサで片方ずつ順に実行する必要があるが、MIMDであればプロセサごとに実行する命令を変えることもできる。

-

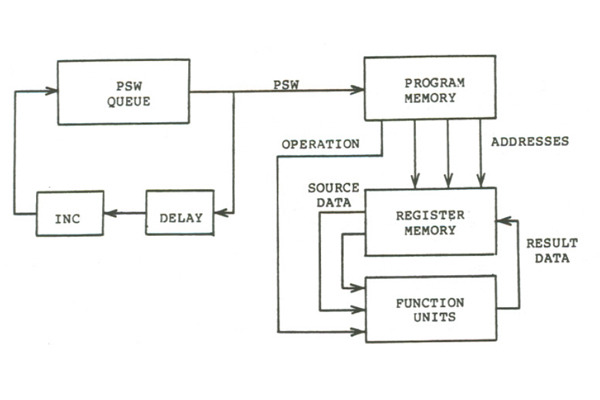

図3.13 CM-5のノードの構成。自社開発のプロセサを止め、SunのSPARC CPUを使い、4個のWeitekのFPUを使ったベクタユニットを持たせた (出典:J.Palmer; G.L.Steele、"Connection Machine model CM-5 system overview"、4th Sympo. on the Frontiers of Massively Parallel Computation、1992)

図3.14にベクタユニット部のブロックダイヤグラムを示す。演算部は乗算器と加算器が直列に接続されており、積和演算を行えるようになっている。さらに、1語(64bit)の中の"1"の個数を数えるPopulation Count演算器を持っている。

そして、アドレスジェネレータは、ベクタ演算のための、先頭アドレスに指定された増分を加えたアドレスを発生する。

-

図3.14 CM-5のベクタユニットのブロック図。ベクタを一定間隔でアドレスするためのアドレス発生器、レジスタファイル、そして浮動小数点演算の加算器と乗算器を持つ (出典:Connection Machine model CM-5 system overview)

(次回は12月13日に掲載します)