PCI Express 7.0が正式にリリース

PCI-SIGは6月11日(米国時間)、「PCI-SIG Developers Conference」を例年通り開催した。これに合わせた行われたPress Conferenceにおいて、PCI Express 7.0(PCIe 7.0)のSpecification 1.0がリリースされたことが明らかにされたので、その内容をご紹介したい。

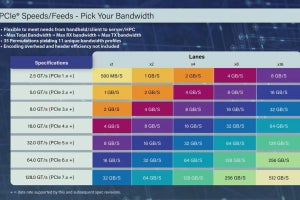

PCI Express 7.0はPCI Express 6.0の信号速度を倍増させた形である。つまり信号速度そのものは64GHzとなり、ここにPAM4変調を組み合わせて128GT/secの転送速度を実現した格好だ。1レーンあたり128Gbps(厳密には128b/130b Encodeを利用するのでなので126.03Gbpsだが)=16GB/secであり、x16レーンの場合は片方向で256GB/sec、双方向合計だと512GB/secもの帯域に達する(Photo01)。

PCI Express 8.0についての取り組みも開始

これに併せて、PCI Express 8.0のPathfindingも開始されたことが表明された。ただ現状はそれが完全にOpticalベースに置き換わるのか、それとも7.0の延長でElectrical/Opticalの併用になるのかを含めて「何も決まっていない」との事で、こちらに関しては何かしらの話が出てくるまでもう少し時間が掛かりそうである。ちなみにAl Yanes氏(Chairman兼CEO)曰く「(個人的には)Electricalでも出来たらいいなと願っている」そうだ。

話を戻すと、PCI Express 7.0では信号速度の倍増に加え、新たにUnordered I/Oと呼ばれる機能が追加されたことも明らかにされた。これについては近日中にWebinarの形で詳細が公開される予定との事である。

Specificationが公開されてから始まるのはInteroperability Testであるが、このためにはCompliance Programが必要になってくる。すでにPCI Express 4.0/5.0に関してはスタートしているが、PCI Express 6.0に関しては今年中にCompliance Programを実行できるIntegrator Listが公開予定との事。一方PCI Express 7.0についてはPre-FYIが2027年、Integratorの方は2028年と結構先である(Photo02)。

現実問題として今PCI Express 7.0のSpecificationが公開されたとして、これをインプリメントしたI/F IPが登場するのは、一部のベンダーは今年後半(例えばSynopsysはすでにDraftに基づいたPCI Express 7.0 I/F IPをリリースしているから、こういうメーカーはDraft→1.0の変更点の修正だけでリリース出来る)だが、多くのベンダーはこれからスタートであり、そうしたメーカーのI/F IPが完成するのは2026年に入ってから。試作品のテープアウトは2026年後半で、動作するシリコンが出てくるのは2027年という事になるだろう。そう考えると、まず動作するシリコンでPre-FYI Testを行うのは2027年というタイムラインは結構現実的ではある。

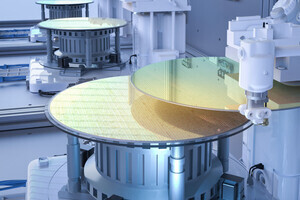

PCIe 6で光ファイバーの接続を可能とするECNがリリース

次にECN(Engineering Change Notice:技術変更通知)について。PCI Express 5.0はECNを統合した形でPCI Express 5.1が、同様にPCI Express 6.0はECNを統合した格好でPCI Express 6.3がすでにそれぞれリリースされているが、今回、光ファイバーによるPCIe接続を可能とするOptical Aware Retimer ECNを統合したPCI Express 6.4がリリースされたことが発表された(Photo03)。

このOptical Aware Retimer ECNでは、

- 既存のPCI Express 6.4/7.0の仕様に準拠したSwitchやRoot Complex、End-pointの間の接続にOptical Cableをシームレスに利用できる

- Rack/Pod間の接続に利用できる様に到達距離が拡張

- Electrical/Opticalの2つのドメイン間のMultiplexingおよびData Mappingが可能

- Copper Cableを利用するElectrical Solutionよりコンパクトに実装可能

といった特徴を持つとしている。

名前からしてRetimerの仕様を拡張し、Opticalでの利用も念頭に置いたという事かと思われる。従来だと、Optical Cableを利用する場合も、伝達特性などはCopper Cableに合わせる形で実装が行われていたが、今回のECNでCopper Cableの場合とOptical Cableの場合で仕様が変わる様になったのかもしれない。

ちなみに質疑応答の中でPCI Express 7.0のTarget Process Nodeに関しては「具体的なNodeを念頭に置いている訳では無いが、出来る限り最新のプロセスを、と答えている。これは64GHz PAM4という高速信号処理は最新のノードでないと厳しいからだ。ただProcess NodeだけでなくPackagingやConnector、Channelの構成など様々なものが重要であり、これらの要素の組み合わせでターゲットとなる速度(128GT/sec)が実現できるかどうかが決まる」という返答であった。変な例かもしれないが、PCI Express 5.0対応NVMe SSDは12nmあたりだと爆熱で、7nmにして何とか発熱が抑えられた。PCI Express 6.0では恐らく5nmか下手をすると3nm、7.0は最低3nmで現実問題としてはGAAの2nmないしそれ以下のプロセスでないと厳しいかもしれない。

ただ、ではいつPCI Express 7.0を搭載した製品が市場に登場するか? と問われて「一般論として仕様が公開されてから2.5~3年程度で市場に投入されてきた」としており、ということは2028年~2029年の時間軸ということになる。この辺りであれば、もうGAAプロセスが一般的で、プロセスノードも2nm未満であろうと考えられる。

CXLやUCIeなどもPCIe 7.0への対応が進む可能性

今回の発表を受けて、まずCXLもPCI Express 7.0に対応した仕様のバージョンアップが行われることになるかと思われる。またUCIeも現在は32GHzまでの信号しか定義が無い(PCI Express 6.0は32GHzと言いつつPAM4変調なのでちょっと厳しい気はするが)。なので今後PCI Express 7.0に向けて64GHzの信号を通せるような規格が追加される様に思われる(でないとUCIeのPHYの手前にGearboxを入れて速度を変えないといけなくなる)。

しかしPCI Express 7.0は実にスムーズというか、まったく遅れが無い(というか、2022年の発表時のタイムラインそのまま)なのにはちょっとびっくりである。

そういえばその2022年に電気的特性を聞かれて「仕様策定までには3年ある。その間の技術の進歩でこの辺りを解決できる事に期待したい」という投げっぱなしジャーマン的返答が帰って来たのだが、今回同じ質問がやはり出て、その返答は「細かいパラメータまで私から説明する事は出来ない。後でDevConで公開されたスライドのうち、出せるものがあれば送る」という曖昧な返答しかかえってこなかった。これもなんかそのうちWebinarで説明がありそうな気がする(一応筆者もリクエストは出してあるが、果たして何かしらの返答があるかどうか、ちょっと疑問だ)。