東京大学 生産技術研究所(東大 生研)と芝浦工業大学(芝浦工大)は3月17日、パワー半導体のスイッチング損失を自動で低減するとして2023年3月に発表していたゲート駆動ICチップについて、現在パワーデバイス市場で広く採用される“3本足パッケージ”への適用を可能にし、同チップの適用範囲の大幅な拡大に成功したことを発表した。

この発表に際し東大 生研はオンラインで記者説明会を実施。開発を主導した東大 生研の高宮真教授が登壇し、今回発表された新技術のメカニズムや、エネルギー利用の観点からパワーデバイスへの注目が集まる将来の社会に与えるインパクトについて説明した。

なお今回の研究成果は、東大 生研の高宮教授、同・梁耀淦特任研究員、芝浦工大 工学部の畑勝裕准教授らの研究チームによるもので、新エネルギー・産業技術総合開発機構(NEDO)の委託事業「省エネエレクトロニクスの製造基盤強化に向けた技術開発事業」により得られた。また詳細は、3月16日から20日まで米・アトランタで開催されている国際学会「IEEE Applied Power Electronics Conference and Exposition (APEC) 2025」にて発表された。

2023年に発表した損失低減技術の適用範囲を5倍に拡大

省エネルギー化への要求が高まる昨今、パワーエレクトロニクス機器の分野では、パワー半導体、特に大電力のスイッチとして機能するゲート端子を有するIGBTやパワーMOSFETについて、エネルギーの低損失化を実現するための研究開発が活発に進められている。

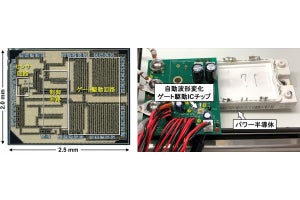

そうした中で高宮教授が率いる研究チームは、パワー半導体そのものではなく、パワー半導体の「ゲート駆動」を最適化し、“使いこなし”の観点からスイッチング損失の低減を目指してきたとのこと。そして2023年3月、パワー半導体のゲート端子を駆動する電流波形を適切なタイミングで自動的に複数回変化させる「自動波形変化ゲート駆動ICチップ」を開発し、1チップ化したゲート駆動回路によるスイッチング損失の低減に成功していた。このICチップは、ゲート駆動回路・センサ回路・制御回路を統合し、従来のゲート駆動ICチップと置き換えるだけで利用できるものだったというが、高宮教授によるとこの技術は、パワー半導体の中でも“4本足パッケージ”のデバイスに適用範囲が限られていたという。

パワー半導体のパッケージは、研究チームの開発技術が適用されていた4本足パッケージと、“3本足パッケージ”のものに分類される。前者はゲート・エミッタと出力ピンからなる3本足パッケージに、駆動回路のインダクタンスを低減させるケルビンエミッタを加えたもので、スイッチング速度の向上およびスイッチング損失の低減を実現している。ただ一方で、シンプルな3本足パッケージに比べるとコストが高いという課題があり、現在の市場における主要パワー半導体メーカーの製品を見ると、全体のおよそ8割を3本足パッケージの製品が占め、研究チームの技術が適用可能な4本足パッケージは2割程度にとどまっていたとする。

そうした背景から研究チームは、パワー半導体のスイッチング損失を低減するゲート駆動ICチップについて、3本足パッケージにも適用可能な形での実現に向けて研究を開始。そして今般、IC内部のセンサ回路を改良することで、ゲートを駆動させる電流をセンシングするため、ゲート端子に挿入されたセンス抵抗の両端電圧を検出する新たな方式を採用。ゲート駆動電流の変化をセンシングしてその強弱をクローズドループでフィードバック制御し、ゲート駆動回路で出力電流を最適化することで、スイッチング損失の低減を実現したとしている。

電流や温度の変化にも対応する安定した低減効果を確認

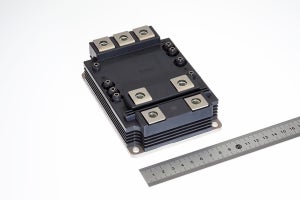

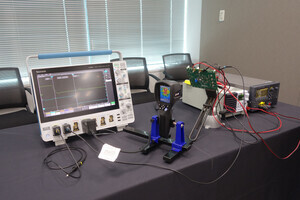

なお高宮教授は、今回開発されたICチップの特徴として、負荷電流や温度などの動作条件が変動した場合でも、ゲート駆動電流のタイミングを自動で調整できる点を挙げ、環境を問わず安定的にスイッチング損失低減の効果を得られるとする。研究チームによる性能実証試験では、市販のシリコン(Si)パワー半導体を用いた600Vでのスイッチング試験を行ったといい、3条件の負荷電流(20A・50A・80A)および3条件の温度(25℃・75℃・125℃)の合計9条件における実測の結果、すべての条件で従来のゲート駆動方式に比べてスイッチング損失の自動での低減に成功したとのこと。またその損失低減率は16%から30%の範囲だったといい、2023年の発表技術では最低で一桁だった損失低減率の安定化が実現されたとした。

また、センサ回路と制御回路、そしてゲート駆動回路の3機能を1チップに集約したこのICチップは、搭載の際に従来のゲート駆動ICチップとそのまま置き換えが可能であるため、省スペース化・低コスト化にも貢献可能。加えて、Siや炭化ケイ素(SiC)などさまざまな素材を用いたパワー半導体にも対応しており、幅広い用途での適用が期待されるという。

高宮教授は今回の発表技術について、現在も研究開発の段階であり、実用に向けてはICチップ内のセンサ回路の駆動を自動化させるなど、アップデートを続ける必要があるとするものの、「将来的には半導体メーカーに向けて、今回の技術の採用に向けた働きかけを行っていきたい」とコメント。省エネルギー技術の普及がさらに進んでいく中、パワーエレクトロニクス機器の高効率化を通じて温室効果ガス排出削減に貢献していくことが期待されるとしている。