PCI-SIGは例年6月にDeveloper Conferenceを開催するが、今年は当然ながらオンサイトミーティングを開催出来る状況ではなく、Developer Conference/Annual Meetingともにオンラインでの開催となった。

これに併せて、Press Conferenceも6月3日にオンラインで開催されたので、まずはこの内容を簡単にご紹介したい。

PCIe Gen4/PCIe Gen5の現況

まず既存のPCI Expres Gen4(PCIe Gen4)に関しては、もうすでに広範に製品の出荷も始まっており、テスト装置なども多数で回って、安定して利用できる環境になっているとする(Photo01)。

-

Photo01:皮肉なことに、PCIe Gen3までは市場を牽引する形で率先してプラットフォームを提供しているIntelが未だにPCIe Gen3のプラットフォームを出せていないが、それ以外のベンダー(AMDもそうだしArmベースSoCなど)はすでにPCIe Gen4に移行している

ついで2019年5月に標準化が終わったPCIe Gen5であるが、こちらもすでにIPの提供を始めるところも出てきており(例えばSynopsys)、またテスト機材もそろい始めて(例えばアンリツのMP1900A)おり、製品への実装を開始出来る状況にあるとされる(Photo02)。

-

Photo02:PCIe Gen5については、もうすでにこれを前提にした規格(例えばCXL)が存在するから、概ね24か月以内に製品が出てくるだろうというのは現実的に見える。問題はIntelが間に合うかどうか…

これを支えるのがCompliance Programである。PCIe Gen4向けのTest Specificationは2019年6月にリリース、Official Testも同8月に開催されており、現時点で85製品がラインナップされている(Photo03)。ちなみにGen 5に関してはまだTest Specificationの策定中だそうで、これは2020年後半にリリースになる予定との事だった。

ここでちょっと余談なのだが、リストを眺めていると、Root ComplexおよびSystems with CEM Slot(s)にIntel Processor PCI Express Controller - Device ID(347A,347B,347C,347D)なるものが2020年4月に登録されていた。さてこれは何だろう? というと、恐らくはIce Lake-SPだと思うのだが、少なくとも今のところ公開されていない事は確かである。

PCIe Gen6は2021年に登場予定

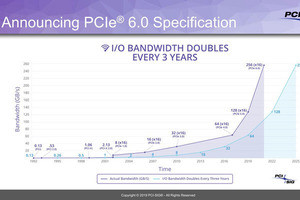

さて、ここからは今後の話。PCI Expressは概ね3年に2倍のペースで帯域を増やしてきていた(Photo04)。

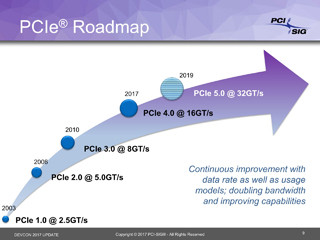

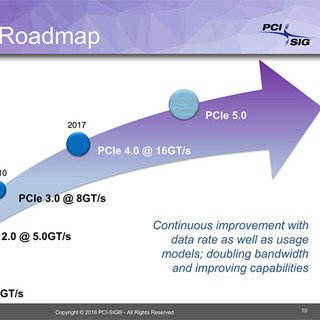

これについでPCI Express Gen6(PCIe Gen6)が2021年に投入される予定になっている(Photo05)。現状はまだDraft 0.5が出た段階で、今年中にDraft 0.7をリリースする予定となっている。最終的なリリースは2021年度を予定しているとの事だ。

特徴としては、

- PAM4を採用する事で、転送速度そのものは据え置きのまま帯域を倍増。

- FECとCRCを併用してエラー訂正

- 新たにFLIT(Flow control unit)と呼ばれる技術を採用

というあたりになっている

さて説明はこの程度だが、ChairmanのAl Yanes氏に「ではその次はどうするのか?」と確認したところ、「その議論は2021年に始める予定だ」とあっさり躱されてしまった。