Hot Chips 28において、Samsung Electronicsは自社開発の「Exynos M1」プロセサコアを発表した。

|

|

Exynos M1プロセサコアを発表するSamsung Austin R&D CenterのVP兼CPU ArchitectのBrad Burgess氏 |

Samsungは自社スマートフォン(スマホ)「Galaxy S6」までは、ARMのCortex-A57とA53コアを搭載していたが、最新世代の「Galaxy S7」の一部モデルから、Exynos M1とA53コアという構成に変更した。

ARMの命令セットだけをライセンスして、チップは論理設計から自社開発すれば、ARMからライセンスするコアより高性能のコアを作ったり、自社の重視する機能を充実するなどで、他社のスマホとの差別化が可能になる。 また、コアが高性能化するにつれてARMのコアのライセンス料も高くなっており、一世代ならまだしも、数世代も資産を引き継いで開発することを考えると、自社開発の方がコストが安いという考慮もあると思われる。

このため、Samsungだけでなく、Apple、QualcommやNVIDIAもARMコアの自社開発を行っている。また、Applied MicroやCaviumなどはサーバ用の高性能ARMコアを自社開発している。

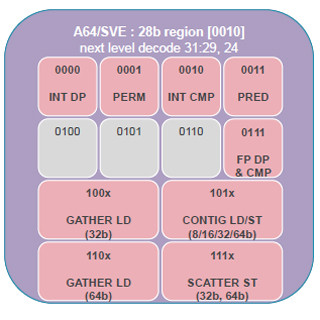

M1プロセサは、ARMv8.0アーキテクチャのプロセサで、AArch64とAArch32の命令をサポートしている。M1はSamsungがゼロから開発した最初のプロセサで、3年間で開発したという。要件定義からテープアウトまで3年というのは、まあ、速い方である。

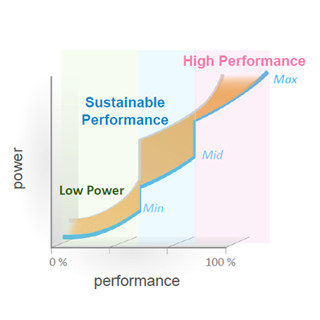

Samsungの14nmのFinFETプロセスを使い、2.6GHzクロックで、コアあたりの消費電力は3W以下となっている。4コアの設計で、業界でも最高クラスの設計であるという。

|

|

Samsung M1プロセサの概要。M1はSamsungがゼロから開発した初めてのARMプロセサである (この記事のすべての図は,Hot Chips 28におけるBurgess氏の発表資料のコピーである) |

M1プロセサは、先進的な分岐予測を使い、4命令を並列にデコードし、4マイクロ命令(μOP)を並列にディスパッチ、リタイアすることができる。命令の実行は完全なOut-of-Orderになっており、マルチ・ストライド/マルチ・ストリームのプリフェッチを行うことができる。そして、低レーテンシで低電力のキャッシュを備えている。ということで、かなり意欲的な高性能向けのプロセサ設計となっている。

分岐予測は、パーセプトロンを使った分岐予測を行い、1サイクルに2つの条件分岐命令を扱える。64エントリのマイクロTLBと4KエントリのメインTLBを備え、64エントリのCall-Returnスタック、間接分岐の予測機構、ループデテクタなどを備え、他のプロセサの論文に出てくるほとんどの予測機構を備えている。

M1の命令キャッシュは64KB、4wayの構成になっている。ラインサイズは128バイトである。命令の読み出しはサイクルあたり24バイトで、これは6命令に相当する。Out-of-Order実行を考えると、命令の先読みが不足ではないかという感じもするが、命令がさくさく流れているときはOut-of-Order実行も不要で、流れの悪い時は、たくさんの命令が溜まり、Out-of-Orderのスケジュールが生きてくるようになるので、これでも良いのかもしれない。

また、ループデテクタを持っているので、命令バッファに入っている命令を再利用できる場合は、命令キャッシュから読み出す必要は無い。

4命令をデコードし、4μOPをディスパッチし、4μOPをリネームし、4μOPをリタイヤするOut-of-Order実行を行う。リオーダバッファは96エントリである。

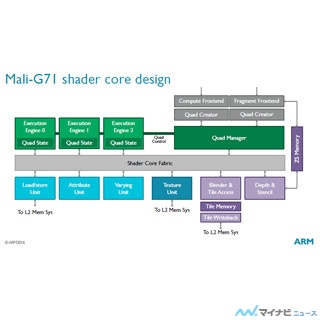

整数演算器は7つのユニットがあり、最大7μOPを並列実行できる。ただし、ストアアドレスの計算ユニット、ストアデータを用意するユニットなども含まれているので、一般的な命令で言えば、最大4命令という感じである。スケジューラはユニットごとに分かれており、全体で58エントリを持つ。物理レジスタファイルのエントリ数は96エントリである。つまり、64エントリはリネーム用に使われている。

|

|

整数演算部は、7つのμOPを並列に実行できるが、通常の命令で言えば4命令並列という感じである。スケジューラは実行ユニットごとに分離された構造で、合計58エントリ。物理レジスタファイルは96エントリを持つ |

浮動小数点数演算部は、32エントリの単一スケジューラを持ち、FMAC(Multiply-Accumulate)演算器とFadd加算器を持つ。物理レジスタファイルの数は96個である。FMACのレーテンシは5サイクル、MULだけならば4サイクルで実行できる。そして、Faddは3サイクルである。このあたりのレーテンシは、まあ、普通である。

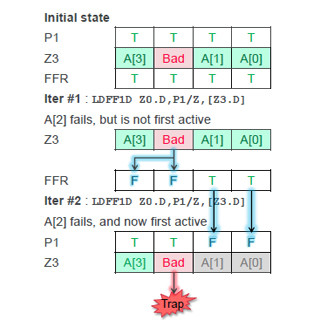

ロード/ストア系は、32KB、8wayの1次データキャッシュを持っている。ラインサイズは64バイトで、ロードのレーテンシは4サイクルである。Out-of-Orderのロード、ストアを行うことができ、最大8個のキャッシュミスを抱えた状態で、その次のアクセスを処理できるようになっている。

TLBは32エントリのdTLBと1024エントリのL2TLBを持つ。そして、マルチ・ストライドのプリフェッチャーを備える。

また、L1データキャッシュには、ECCが付けられており、1bitエラーを訂正できる。

|

|

ロード/ストア系は、32KB、8wayの1次データキャッシュを持っている。ラインサイズは64バイトである。Out-of-Orderのロード、ストアが行える。ロードのレーテンシは4サイクル。データ保護のため、ECCが付けられている |

2次キャッシュは2MB、16way構成で4バンクに分かれている。レーテンシは22サイクルで、バンド幅は16バイト/サイクル/CPUである。

パイプラインは、次の図に示すように、整数系の演算命令の場合で15段。ロード命令の場合は20段+L2キャッシュのアクセス時間となる。