Lattice Semiconductorは5月30日、モバイル機器のイメージセンサやディスプレイの主要プロトコルをサポートするプログラマブルブリッジングデバイス「Lattice CrossLink」を発表した。

同製品は同社が2015年に買収したSilicon Imageの技術を活用したもので、同社ではFPGAの柔軟性とASSPの機能性/効率性を両立させたプログラマブルASSP(pASSP)という新たなカテゴリに位置付けている。

カメラやディスプレイを搭載したモバイル機器の多くは、相互のインタフェースの種類やレーン数が一致しないため、ブリッジを使って接続性を確保している。CrossLinkでは、12Gbpsの帯域幅で最高4K UHDの解像度に対応するMIPI D-PHYやMIPI CSI-2、MIPI DSI、CMOS、sub LVDS、LVDSなどのインタフェースをサポートしており、1チップで各種の映像分野に関するブリッジを実現することが可能だとする。

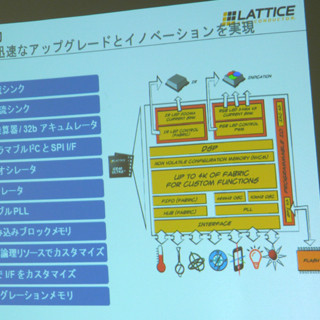

このインタフェースとしては、プログラマブルI/OとハードコアのMIPI D-PHYを用意。リファレンスIPを活用することで、各種のディスプレイ/カメラインタフェースのブリッジをFPGAの知識がなくても可能とするほか、FPGAファブリックとして5936LUT、180KビットブロックRAM、47Kビット分散RAMを搭載しており、多重化や統合、分離といったビデオ処理などを行うことも可能。これにより、例えば、ステレオカメラと1チップで接続し、多重化や統合処理を行い、後段のイメージプロセッサにD-PHY経由でデータを送信することが可能となる。

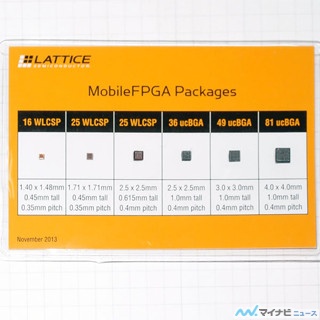

また、小型機器への搭載にも対応することを目的に最小6mm2のWLCSPパッケージをオプションとして用意している。さらに、消費電力もアクティブ状態で約100mWと競合製品に比べて最大50%低く抑えているほか、スリープモードにも対応しており、モバイル機器で要求される低消費電力性能を実現しているとする。

なお同製品はUMCの40nmプロセスを採用し、2016年8月の量産出荷を予定。開発ツールは同社の「Lattice Diamond」が対応しているという。