東北大学(東北大) 電気通信研究所の吹留博一助教、末光眞希教授および尾辻泰一教授の研究グループは、Si基板の面方位による、Si基板上に成長させた次世代電子材料グラフェン(GOS)の多機能化(金属性・半導体の切り分け)に成功し、GOSを用いたトランジスタの集積化も可能であること示した。現在の半導体集積技術を用いてグラフェンの多機能化・集積可能性を示したことは、グラフェンの多機能集積回路への道を拓いたということを意味する。同成果は、日本原子力研究開発機(JAEA)量子ビーム応用研究部門の寺岡有殿 研究主幹、同吉越章隆 研究副主幹、高輝度光科学研究センター(JASRI)利用研究促進部門の木下豊彦 主席研究員、同 小嗣真人 研究員および同 大河内拓雄 研究員との共同研究によるもので、応用物理学会の学会誌「Applied Physics Express」(オンライン版)に掲載される。

炭素の二次元層状物質であるグラフェンは、Siの100倍以上のキャリア移動度を有し、かつ熱的・化学的にも安定な物質であるため、Siに置き換わる次世代デバイス材料の1つとして、実用化に向けた開発が進められている。

研究グループでは、これまで既存Siデバイスの製造技術を最大限に活用することを目指し、Si基板上に単結晶SiC薄膜を成長させ、このSiC薄膜表面にグラフェンを形成するグラフェン・オン・シリコン(GOS)の開発を進めてきている。

すでにGOSを用いた電解効果トランジスタ(FET)の開発なども進めており、同トランジスタは2000cm2/Vs以上という、Si半導体と比較して2倍のキャリア移動度を持つことが確認されている。GOS技術は半導体プロセスをそのまま利用できるため、実用化が期待されているが、単にキャリア移動度が高いというだけではなかなかSiデバイスを置き換えることはできないことから、研究グループでもGOSでしか発現されない技術などの開発を行ってきていた。

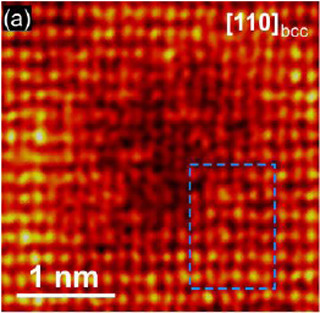

今回の研究では、これはSPring-8においてJAEA専用ビームラインBL23SU設置のリアルタイム光電子分光装置および理研ビームラインBL17SUせっちの 分光型光電子・低速電子顕微鏡を用いることで、GOS技術に用いられるSi基板の面方位を選択することで、グラフェンの表面・界面構造およびバンド構造が制御可能であることを明らかにした。

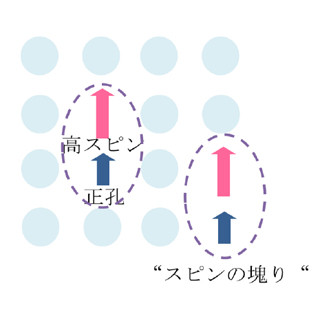

これまで高価なSiC結晶基板の面方位を選択することで、グラフェンのバンド構造制御が可能であることは知られていたが、安価で大面積なSi基板上で同様の制御が可能になることが明らかとなったのは今回の研究が初めてだという。

この成果はグラフェンのデバイス特性(キャリア移動度、バンドギャップ)をSi基板上で自在に制御することが可能になることを意味するもので、デバイスの応用用途として電子や光に適したグラフェンの製造が今後できるようになる可能性を示すものだという。

さらに研究グループでは、比較的大面積なGOS(7mm×40mm以上)を作成し、それを用いて複数のFETを試作して評価した結果、それらの素子特性のバラつきが少ないことを確認した。トランジスタサイズは数μm程度で、集積度は低いものの、この結果はGOSを用いた集積回路の作成が将来的に可能であることを示すものだと研究グループでは説明している。

これらの成果を踏まえると、半導体プロセス技術を用いることで、1枚のSi基板上にさまざまな面方位のSi面を容易に作り出すことも可能となるため、将来的にはSi基板上に三次元的に作りこまれた多機能なグラフェン集積素子(3D-GOS)の実現も期待できるという。

最新のデバイスシミュレーションでは、チャネル長が20nmまで縮小されたグラフェン集積回路がSi集積回路よりも1桁高速の論理動作をする可能性が示されており、今回の成果を踏まえて、今後、GOS技術をさらに進展させていくことで、そうした集積回路が実現できる可能性が出てきたこととなるため、研究グループではまだ多くの研究課題が残されているものの、GOS集積回路がSi集積回路の代替物以上のものになる可能性が出てきたとしている。