産業技術総合研究所(産総研)は、0.5nmの薄い高誘電率ゲート絶縁膜を製造する技術を開発したことを明らかにした。2010年12月6日~8日かけて米サンフランシスコで開催されている半導体デバイスに関する国際学会「IEDM 2010」にて発表された。

プロセスの微細化によって生じるトランジスタのゲート絶縁膜の漏れ電流低減を図るため、世界中の半導体メーカー、大学、研究機関などが高誘電率材料を用いたゲート絶縁膜の研究開発を行っており、現在、シリコン酸化膜(SiO2)換算膜厚で1nmのゲート絶縁膜が開発され、すでに同技術を用いた集積回路も製品化されている。半導体業界のロードマップとしては、2013年以降には0.65nm、2015年には0.53nmの薄さを必要としており、世界中でこの目標の実現に向けた研究開発が現在も進められている。

そのような状況の中、産総研も高誘電率ゲート絶縁膜の研究開発を行ってきた経緯があり、原子層成長技術と急速熱処理技術を組み合わせた不純物低減技術の開発、高誘電率材料とシリコン酸化膜の界面に発生するダイポールがトランジスタ動作のしきい値電圧や移動度低下に及ぼす影響の解明などの成果を発表してきた。

今回開発された技術は、高誘電体材料の結晶膜の合成方法を新たに考案し、開発に至ったもの。これまでにも結晶膜で高誘電率ゲート絶縁膜を作る試みは世界中の企業や研究機関で行われており、すでに研究用途の特殊な成膜方法を用いて、結晶膜の優秀性を示す成果も得られている。しかし、生産用途の製造プロセス装置で高誘電体材料の結晶膜を合成すると、低誘電率層の生成による膜厚増加や漏れ電流の増大が発生するため、実用レベルの性能をもつ絶縁膜の作製は困難とされていた。

そこで同研究チームでは、生産用途の装置を用いながら、結晶化の過程を改良することで、従来解決されていなかった問題の克服に取り組んだという。

図1の左は、今回実現した、Si基板上に合成した高誘電体材料であるHfO2結晶膜の高分解能電子顕微鏡写真。基板のSi結晶の原子配列に対して、HfO2の結晶の原子配列が整合して成長している様子が現れている。

また、図1の右は、Si基板上に合成したHfO2結晶膜にゲート電極を形成して測定したSiO2膜換算膜厚と漏れ電流値の関係で、今回開発した技術では、Si酸化膜の場合と比較して6桁の漏れ電流の低減を実現した。最も薄い場合では0.5nmの性能を1A/cm2の漏れ電流で達成しており、開発した技術が実用化されれば、今後10年にわたるゲート絶縁膜の開発にめどが立つと研究チームでは考えているという。

|

|

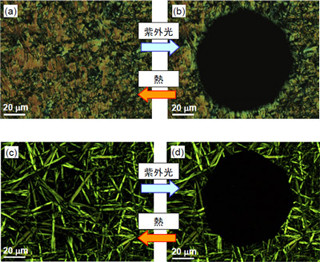

図2 開発した高誘電率結晶膜(HfO2)の合成方法。1でSi基板上に非晶質状態のHfO2膜を堆積、2で基板からの熱伝導を利用して界面からの結晶成長を促進、そして3で隙間の無い、ち密な結晶膜が完成される |

さらに、今回開発されたプロセスのモデルを図2に示す。最初にSi基板上に原子層成長法で非晶質のHfO2膜を堆積。続いて高温熱処理で非晶質膜を結晶化させる処理を行うが、このときに、Si基板からの熱伝導を利用して、基板界面からの結晶化が始まるようにする。これにより、界面に低誘電率層が生成することを抑止できる。加えて結晶成長の方向がそろっていることで、隙間のない、ち密な結晶膜が得られ、漏れ電流の増大も抑えることが可能になるという。

研究チームでは、今回開発した技術について、現行の半導体デバイスの製造現場と同様の材料ならびに同等の製造装置を用いて実現したものであり、実用化への困難が少ないと考えており、今後は作製した構造のプロセス耐性、電気特性のバラつきや信頼性を系統的に試験することで、将来の低消費電力デバイスの開発につなげたいとしている。