Freescale Semiconductorは、6月21日(米国時間)より開催している同社のテクノロジーフォーラム「FTF(Freescale Technology Forum)Americas」において、Powerアーキテクチャベースの組み込みプロセッサ「QorIQ」のラインナップ拡充を発表した。

|

|

|

フリースケール・セミコンダクタ・ジャパンのネットワーク、インダストリアル、コンスーマ・マーケティング本部部長の岩瀬肇氏 |

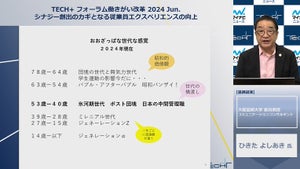

「半導体産業にはムーアの法則が存在するが、IPトラフィックの伸び率はそれを超えるという予測が立っている。しかし、ネットワークに対する設備投資額は低い割合のままであり、効率のよい高性能ネットワークシステムを構築する必要が生じている。しかも、ネットワーク上を流れるトラフィックの種類もビデオ、Webメール、ビジネス用途などさまざまなものとなっており、それらを高速に処理していくためには高い処理性能がサーバなど各種ネットワーク機器に求められる」(フリースケール・セミコンダクタ・ジャパンのネットワーク、インダストリアル、コンスーマ・マーケティング本部部長の岩瀬肇氏)ということであり、それらを処理するための高い処理性能を持つプロセッサが求められていた。

|

|

|

|

ムーアの法則による半導体の性能向上を超す勢いでネットワークトラフィック量が増大していくが、それに見合うだけの設備投資は望めないのが現状のため、同程度の金額の機器1つ1つの性能向上で対応を図っていくしかないというのが問題となってきている |

|

現状のネットワーク機器における技術課題は2つあると同氏は指摘する。1つはネットワーク制御系で、「分割しにくい制御系処理、高性能化と省電力化要求のバランス、そしてより広いメモリ空間への要求などが存在しており、こうした課題を解決するためにはコア単体(単一スレッド)の高性能化が求められている」とする。もう1つは制御系とデータ処理系の統合で、「大量のチャネル、ユーザーを扱うデータ系処理を実現しつつ、消費電力を押さえて、ボード面積やBOMコストの削減という問題の両立が求められており、こうした課題を解決するためには高度に統合化された省電力マルチコアを活用する必要がある」とする。

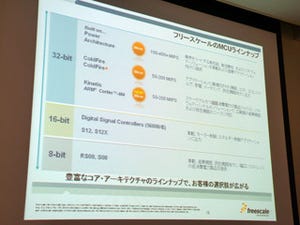

こうした課題を解決するために開発されたのが、QorIQファミリの中でも最上位に位置する64ビットISA(Powerアーキテクチャv2.06準拠)をサポートし、アドレス可能なメモリ空間を64GBまで増加させた64ビット対応の「e5500」コアを搭載した「QorIQ P5」ファミリとなる。P5ファミリには、2コアの「P5020」と1コア「P5010」の2つの製品がラインナップされる。

e5500は最大2.5GHzのコア周波数を実現しており、現行世代のPowerアーキテクチャコア(e500mc@1.5GHz)比で2倍のシングルコア性能を実現できる。また、既存のソフトウェアとの互換性を維持するハイブリッド32ビットモードを採用。これにより、ソフトウェアの設定で32ビットモードと64ビットモードの切り替えが可能となり、64ビットアーキテクチャへの移行を容易に行うことが可能になるという。

また、併せて低消費電力を維持しながら、クアッドコアを活用することで複数機能などの制御を可能とする「QorIQ P3」ファミリも発表された。P3ファミリ製品となる「P3041」は、e500mcコアを4つ搭載し、各コアは1.5GHz駆動で、約2.5DMIPS/MHzの性能を実現しながらも12W未満の消費電力を維持することが可能だ。

P5およびP3ファミリがQorIQとして追加されたことで、これでP1~P5までのすべてのQorIQのラインナップが揃ったこととなり、それぞれの要件に応じて、同じPowerアーキテクチャを活用して設計、製造することが可能となる。また、コア数が異なる場合でも、ソフトウェアの互換性はもとより、ピンの互換性ならびにツールチェーンの再利用性を確保、これによりソフトウェア資産の流用などが容易となり開発費を抑制しながら、高性能なシステムの開発が可能となるという。

|

|

|

|

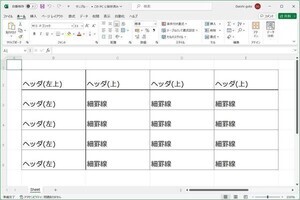

P5とP3ファミリの登場でQorIQは比較的ローエンド向けのP1からハイエンド向けP5までのすべてのラインナップが出揃ったこととなる |

それぞれのQorIQで、ピン互換を確保しており、用途や要求性能に応じて組み変えることが可能 |

P5、P3ともに45nm SOIプロセスを採用しており、低消費電力化を図っている。「P5においても30Wをターゲットラインとしており、通信機器などではこれを切る必用があるため、現状のプロセスのままではコアをこれ以上増やすといった計画はない」(同)とのことだが、プロセスの微細化などによる低消費電力化が進めば、より多くのコアを搭載した製品が出てくる可能性を示唆した。また、64ビットコアのP5以外のファミリへの適用可能性も市場動向としながらもあるとしており、必要に応じてそうした対応を図っていく計画としている。

なお、P5020およびP5010のシミュレーションモデルは2010年7月より出荷を開始、最初のサンプルを2010年第4四半期に出荷予定としているほか、コード生成やデバッグのためのツール「CodeWarrior」も2010年末には64ビット対応を終える予定とのこと。一方のP3041は、2010年第4四半期にサンプル出荷を開始する予定で、P5010/P5020/P3041のいずれもともに2011年下期からの量産開始を予定している。