GPGPUの性能向上に向けた取り組み

同シンポジウムでは、次世代スパコン、RSCC、RICCといった理研が絡むシステムの話のほか、東京大学 情報基盤センターの石川裕教授による第3世代PCクラスタに相当するオープンスパコン「T2K」の東大での活用事例や、2009年1月28日にFellowとなったNVIDIAのDavid Kirk氏が「NVIDIAの提供するCUDAとGPUコンピューティングの現状」を、富士通研究所の成瀬彰氏が「GPGPUクラスタの性能評価手法」を、長崎大学の濱田剛助教が「単精度190TFLOPS GPUクラスター(長崎大)の紹介」といった講演が行われた。

|

|

富士通研究所の成瀬彰氏 |

中でも富士通研の成瀬氏の講演では、GPGPU単体での性能向上のみならず、GPGPUクラスタでの並列処理時における通信処理の遅延をいかに解決するか、といった話題が提示された。

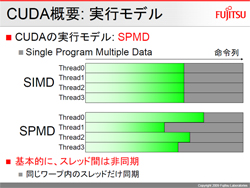

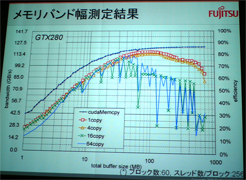

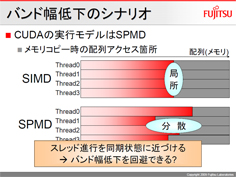

CUDAの実行モデルはSIMD(Single Instruction Multiple Data)ではなくSPMD(Single Program Multiple Data)であり、基本的にスレッド間は非同期となる。メモリアクセス特性は、HimenoBMT(姫野BMT)を対象とした場合、高メモリバンド幅を実現できればベンチマークの高速化とほぼ同義となるため、どれだけメモリバンド幅を取り出すかがポイントとなるが、GPUの実行メモリバンド幅はいつでも高バンド幅を実現できるわけではない。

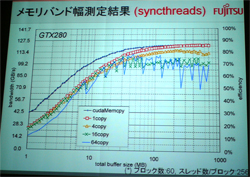

メモリコピーを行う場合、同時に複数コピーすると転送量の増加でバンド幅が低下するほか、ストリーム量の増加でもバンド幅が低下する。そこで、メモリアクセス遅延を測定すると、8MBまでのバッファサイズではランダムアクセスが一定だが、それ以上になると挙動がおかしくなる。「32MBを境界とすることから、恐らくTLBではないか」(成瀬氏)とするが、NVIDIAとしては公式には回答をしておらず、「あくまで、バンド幅低下の問題の原因はTLBスラッシングではないか、という仮説が成り立つにすぎない」(同)とする。

これを解決するには、スレッド進行を同期状態に近づけることで擬似的にSIMD化してやることで転送量増加によるバンド幅低下の解消およびストリーム数増加によるバンド幅低下の改善が図られたとする。

|

|

|

スレッド進行を均一に近づけることがバンド幅低下の鍵になる |

すべてのスレッドの同期はCUDAではできないが、同じブロック内のスレッドであれば同期は可能であり、その結果それなりの性能に向上することが確認された |

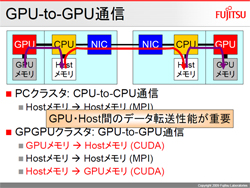

クラスタ環境では、GPUのメモリからCPUのHOSTメモリに転送され、そこからネットワークを介して相手のCPUのHOSTメモリに転送後、GPUのメモリに到達する。このため、GPUとHOSTメモリ間のデータ転送性能が重要になるという。調査の結果では、遅延は10μsecと長めであり、細かいデータを分けて転送するのは得策ではないとの結論に達した。

|

|

|

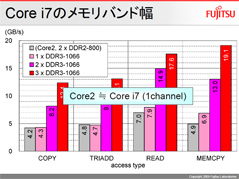

GPU-Host間のデータ転送性能(Pageableの性能が以外に良いのは、実験に使用したCore i7の仕様によるところが大きい) |

ちなみにCore i7のメモリバンド幅はこのスライドの通り(Core 2とCore i7の1チャネル使用がほぼ同じ性能となっている) |

そこで、姫野BMTの逐次版をMPIおよびCUDA化して実証を行った結果、GPUからGPUへの転送は向上したものの、スケーリング則に従うほどではなかったという。

その結論としては、GPGPUクラスタは数ノードクラスなら十分実用的であり、数十以上のノード数の場合には、より高速な通信機構(GPU直接通信やGPU/CPU統合など)のようなアプローチが必要になるかもしれないとした。

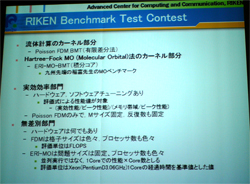

理研BMTコンテストの結果も発表

同シンポジウムでは、「RIKEN BMTコンテスト」と題したベンチマークコンテストの受賞式も開催された。ベンチマークとして用いられるのは「Poisson FDM-BMT」と「ERI MO-BMT」で、計算機の種類・規模は問わない「無差別部門」と使用する計算機を1台だけを使った結果に限定し、Poisson FDM-BMTのみを対象とする「実効性能部門」の2部門が用意されており、今回で6回目の開催となった。

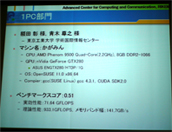

実効性能部門(1PC部門)で最高数値を出したのは、東京工業大学 学術国際情報センターの額田彰/青木尊之両氏。ベンチマークスコアは0.51で、2位との差は0.01程度であったとのことで、「メモリバンド幅に対して高い実行効率のものを選んだほか、富士通研の成瀬氏の論文も活用し、同論文での数値よりも少し上の数値を実現できた」(額田氏)とした。

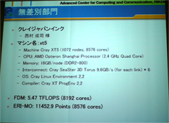

無差別部門を受賞したのはクレイジャパンの西村成司氏。マシンはCrayの米国工場にあるベンチマークマシン「Cray XT5」であり、1072ノードで8576コアを搭載、FDMで5.47TFLOPSを達成している。

なお、理研の姫野氏は、閉会にあたり、「スーパーコンピュータの用途拡大に伴い、性能評価をどのように行うのかが非常に難しくなってきている。そのため、実際のアプリケーションにつながる性能評価をいかに行っていくか、ということを議題にしたワークショップを秋頃に開催したい」としており、現在のスパコンランキングであるTop 500に代わる現実的な指標の模索を行っていきたいとした。