富士通研究所は2月12日、90nm CMOSプロセスを用いた77GHzの高周波信号を処理する車載レーダー用RF送受信ICを開発したことを明らかにした。

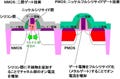

従来、RF送受信ICには高周波特性に優れる化合物半導体が用いられ、低周波に変換した信号を演算するベースバンドICにはCMOS回路が用いられており、1チップに集積することができず、小型化が難しく、チップ価格、実装・試験コストが高いことが課題であった。

特に、RF送受信ICでは送信回路部と受信回路部のそれぞれに77GHzの基準信号を供給する必要があり、2系統に基準信号を分配するための信号分配回路が必要であった。また、雑音を低減するために、それぞれの基準信号を差動信号に変換する変換回路が必要であったが、これらの回路のサイズは大きく、レイアウト配置の最適化や回路全体の小型化が困難だった。

さらに、高周波信号を効率よく伝達するための整合回路には、設計精度を確保しやすい伝送線路素子が用いられてきたが、同素子は信号線とグラウンドを対としたレイアウト構造が必要なため、素子サイズが大きくなり、チップの面積が大きくなってしまうことが問題であった。

今回、同社では、磁界の変化で電流を生成する電磁誘導の原理を用いたトランスフォーマー(変圧器)を用いることで基準信号を2系統の差動信号に分配する回路を開発。これにより、従来の分配回路比で1/100以下のの面積となる縦横80μmの回路を実現した。

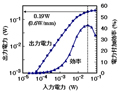

また、設計精度よりも面積低減が重要な回路部位にはCMOS技術の特徴である多層配線構造を利用した小面積のインダクタ素子を伝送線路素子の替わりに適用し、設計精度が必要な回路部位には伝送線路素子を適用する設計技術を確立。77GHzでの正確な動作と回路面積の小型化の両立に成功した。

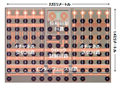

これらの技術を組み合わせたことにより、チップサイズ1.2mm×2.4mmのRF送受信ICを作製した。CMOSプロセスを全体に適用したことにより、信号処理回路を1チップ化することができ、小型化が可能となる。

1チップ化により、従来、RF送受信ICに内蔵できなかった試験機能や環境温度による特性変動の自己調整機能なども、チップ内に搭載できるため、ICチップの実装・試験コストを削減することが可能になるという。

なお、同社では、今回開発したRF送受信ICに、環境温度による特性変動を自己調整する機能やベースバンド回路を内蔵する技術の開発を進め、より高機能・高性能な車載レーダー用ICチップを実現していくとしている。