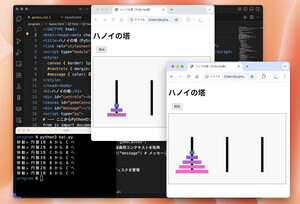

アヴネットは2019年2月15日、「エクストリーム・パワーコンピューティングセミナー」を開催した。これは同社が2018年12月7日に開催した「ハイパフォーマンス・エクストリームコンピューティング・セミナー」に続くものであり、前回のセミナーが「FPGAとはどんなものか」を中心に説明したのに対し、今回は「どんなFPGAカードを利用し、どう使うか」に踏み込んだ内容となった。

GPUと同等の性能を格段のエネルギー効率で実現するFPGA

最初に登壇したのはMAXELER Technologies ビジネス開発&テクニカルアドバイザーの秋元 一泰氏だ。同社はFPGAが搭載されたボードと、この上で動作するMaxeler DFE(Data Flow Engine)と呼ばれるツールを提供するメーカーである。

MAXELER Technologies

ビジネス開発&テクニカルアドバイザー

秋元 一泰氏

このツールの特徴は、このMexeler DFEをMaxJと呼ばれる、Javaに似た高級言語で記述できることで、実際Javaなどに慣れたソフトウェアプログラマであれば、簡単に習得して、この上でシステムを構築できるほか、コーディング量を大幅に減らせるのが特徴とされる。

Javaを含む高級言語との違いは、いわゆるLoopのなかでのBreakにあたる処理が無いことで、そこだけ多少の書き換えが必要となるが、逆にいえば、それ以外は高級言語と同じ感覚でFPGAのプログラミングが可能になるとされる。

このMaxJの活用事例として紹介されたのが東京大学 大規模集積システム設計教育研究センター 教授 藤田 昌弘氏の研究室である。同研究室では、東北大学で開発された「TUNAMI N1」をより高速に実行させるために、津波シミュレータであるTUNAMI N1をGPUとMaxJに移植してその効果を確かめたという。

東京大学

大規模集積システム設計教育研究センター

教授 藤田 昌弘氏

この移植にあたったのは研究室に所属する学生で、プログラミング経験は豊富ながら、VHDLとかVerilogは「そういう名前は聞いたことがある」というレベル、つまりFPGAの知識をまったく持たなかったという。

このTUNAMI N1をNVIDIAのTesla C2075にはCUDAを利用して、XilinxのVirtex6 SX475TにはMaxJを利用してそれぞれ移植を行い、CUDAは1日、MaxJも1週間で移植が終わったとしている。

MaxJの方で多少時間が掛かったのは、さきほどの条件文を投機的実行に書き換える必要があったためだそうだ。

さて、結果であるが、もともとのTUNAMI N1をXeon X5650で実行した場合が1.1GFlops相当、FPGAが46.0GFlops相当、GPUが41.5GFlops相当で、アプリケーションをCPUからFPGAなりGPUに移植するだけで大きな性能改善が見られたとする。

さらに、7200秒分の計算に要したエネルギー消費量はXeonだと1888.8JだったのがFPGAでは77.7J、GPUだと246.5Jとされ、大幅にFPGAがエネルギーの節約になっていることが確認できた。

性能の面ではGPUとFPGAが同程度であるが、性能/エネルギー量では圧倒的にFPGAが秀でており、おまけにMaxJを使うとプログラミングも容易、というのが藤田氏の説明であった。

組み込み用途に適したアクセラレータカードを提供するAdvantech

ついでアヴネット株式会社 エンベデッド事業本部の掛屋 信二氏より、同社が取り扱いを行っている台湾Advantechの製品に関する説明があった。

アヴネット株式会社

エンベデッド事業本部

担当部長 掛屋 信二氏

XilinxのFPGAを使う場合、勿論チップを単体で購入することも出来る(組み込みシステムではこれまで、そういう使い方が多かった)が、サーバーなどの用途ではアクセラレータカードのかたちで導入することが一般的であり、近年では一部の組み込み用途向けにもアクセラレータカードを利用するケースが増えてきた。

こうした用途に向けにXilinxもAlveoというアクセラレータカードを用意しているが、サーバー用途はともかく、組み込み用途では少々使いづらい点がある。その反面、Advantechが提供するアクセラレータは、組み込み向けにも高い利便性を発揮する。

アクセラレータカードとしては、エッジ向けにLow Profile PCI Single SlotのVEGA-4000と、データセンター向けにVirtex UltraScale+をふたつ搭載したVEGA-4001/4002を提供するほか、今後は組み込みに向いたモジュールなども順次提供される予定である。

さて、もともとXilinxではFPGAを利用した動画のエンコード/トランスコード向けのCodec IPを提供しているほか、多くのエコパートナーからもさまざまなビデオCodecが提供されている。こうしたものを組み合わせることで、多様なビデオクラウドへの対応ソリューションを構築できるというものだ。

あるいは先のVEGA-500などではビデオ監視システムと組み合わせての顔認識システムなどの構築の実例もあるという。

ちなみにアプリケーション開発環境としてはXilinxのSDAccelに対応しており、この上でC/C++/HDLで記述することで利用可能(この際に必要となるDSAはAdvantechから提供される)となる。もちろんRTLベースで記述することも可能で、この場合はDMAリファレンスとかクロックソース、PCIe/DDRのピン配置などの必要な情報が提供されるとの話であった。

FPGA実装のポイントを解説

次に登壇したのは、富士通九州ネットワークテクノロジーズ株式会社 ビジネス戦略本部 第四事業部 白石 博昭氏。このセッションではFPGAの実装に関する説明が行われた。

富士通九州ネットワークテクノロジーズ株式会社

ビジネス戦略本部 第四事業部

白石 博昭氏

もともと同社は通信機器向けのシステム開発に長くFPGAを利用してきており、その背景からXilinxのAlliance Program Design ServicesのPremire Member(※)となっている。

(※) 全世界で12社、国内では2社のみがこのグレードを取得している。ちなみにアヴネット自身も米国ではPremire Memberである。

同社によれば、FPGAに既存のアプリケーションをそのまま載せても、性能を引き出すのは容易ではないとする。先述の東京大学の例で条件文の書き換えが必要だったという話があったが、本来高位合成に向いたアーキテクチャと、これを実現するための設計技術が必要というのが同社の見解である。

実際、Machine Learningにおいても、ネットワーク構造ごとに最適なハードウェア構成が変わることは珍しくなく、これを正しく理解して実装しないと性能が出ないとする。

同社のソリューションは、こうした場合にまずネットワークの軽量化を行い、次いでそれに合わせた最適化を行うことで、ソリューションが提供できるというものである。

実際FPGA向けのAI推論器の実装では、他社比で10倍を超える性能改善(画像処理性能で800fps以上)と、1/8以下のLatency(1枚あたり1.2ms未満)を実現できたとしている。

Alveo U200を搭載したDell EMC Power Edgeサーバー

続いてのセッションでは、Dell EMC インフラストラクチャ・ソリューションズ事業統括 製品本部の岡野 家和氏より、FPGAを搭載したPower Edgeサーバーが紹介された。

Dell EMC

インフラストラクチャ・ソリューションズ事業統括 製品本部

岡野 家和氏

テストはともかく、運用段階になるとサポート/メンテナンスの問題は当然考慮に入れる必要がある。これに対してDell EMCでは、2U/4UラックのサーバーにAlveo U200を組み合わせたソリューションをすでに提供している。

ここで重要なのは、これらの機種ではAlveo自身もDell EMCによりサーバーのほかの構成部品と同等のクオリティで動作保証およびサポートが行われるという点で、運用段階におけるメンテナンスをDell EMCに一元管理してもらうことが可能になる。

加えて、同社はOSについてもMLアプリケーションで多く利用されているUbuntuを予め用意しており、アプリケーション開発の際に問題になる環境構築などの手間を最小限に減らせるという話であった。

アヴネット、FPGAを搭載した評価用サーバーサービスを開始

セミナー最後のセッションでは、アヴネット株式会社 ザイリンクス事業本部 小久保 賢二氏が登壇し、FPGAによるアクセラレータ評価環境が紹介された。

アヴネット株式会社

ザイリンクス事業本部

小久保 賢二氏

ここまで説明した通り、「FPGAを利用する環境がありさえすれば」、FPGAを使ってアプリケーションを組むことはもはやそれほど難しくはない。問題はそのFPGAを利用する環境をどう用意するか、である。アクセラレータカードを購入するのはそれなりのコストが必要だし、環境設定にも時間が掛かる。クラウド(たとえばAWSのF1 Instance)では初期費用こそ0だが、インスタンス利用料が掛かる。

そこでアヴネットでは、サーバー機にAlveo U200を搭載し、SDAccel/ML Suite/NG Codecをあらかじめインストールした評価用マシンを無償で貸し出す評価用サーバーサービスを今年4月から開始する。このサービスは、アヴネット内に設置した評価用サーバーを、インターネット回線経由のリモートデスクトップサービスを利用して一定期間無償で利用可能にするというものだ。詳細は4月の開始時期に発表される。

なお、2018年12月よりはじまったこのエクストリームコンピューティングセミナーは、今後も開催が企画されており、次回はAIソリューションをテーマに6月頃の開催を予定しているとのことだ。

ますます広がりをみせるFPGAを活用したアクセラレーション。その最新動向を知るうえでアヴネットからの情報発信には、これからも注目したいところである。

[PR]提供:アヴネット