暁光の実装単位は32PEZY-SC2カードを搭載するブリック

次の図にブリックの写真を示す。1つのブリックには32枚のPEZY-SC2カードと2枚のデュアルXeon Dカード、8枚のInfiniBand EDR HCAカードが搭載でき、4ノード分のハードウェアが収容されている(この図の写真はZS2.0のもので、ZS2.2ではXeon DカードやHCAカードの枚数が増えている)。

次の図の左上の写真はブリックの全景、右上の写真はタンクにブリックを取り付けた状態の写真である。下の写真は、カードをすべて取り外し、ベースキャリアボードやサブキャリアボードが見えている状態である。

-

暁光のブリックの写真。左上が全景。右上はタンクに実装した状態。左下はSC2ボードなどを除いて、キャリアボードが見える状態(これらの写真やカード枚数はZS2.0のもので、ZS2.2ではカードが少し増えているが、外見上、大きな違いはない)

次の図は暁光のノードのブロックダイヤグラムである。ノードは1枚のXeon D-1571カードと8枚のPEZY-SC2カードから構成されており、Xeon DとSC2カードは、PLX社のPEX9797 PCIeスイッチを使って接続されている。

また、各ノードは2枚のEDR InfiniBandのホストチャネルアダプタカード(HCA)を持ち、これらもPCIeスイッチ経由で接続されている。

-

暁光の計算ノードのブロックダイヤグラム。1枚のXeon Dカードと16枚のSC2カードをPCIeスイッチで接続している(この図はZS2.0のものであり、ZS2.2では右側の2つのSC2のブロックが無くなり、それに伴い、PCIeスイッチのネットワークも簡素になっている)

高性能、低電力の計算エンジンPEZY-SC2

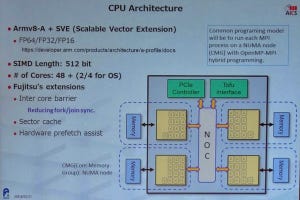

次の図に暁光の計算エンジンであるPEZY-SC2チップのブロックダイヤグラムを示す。中央に256PEのPrefectureが8個あり、クロスバを介して、左右の16個のLLC(Last Level Cache)スライスと接続されている。そして、LLCからは上辺に置かれた4個のDDR4 DIMMに接続されている。

なお、PEZY-SC2チップには2048PEが搭載されているが、64コアは歩留まり向上のための冗長コアとし、演算に使うコアは1984コアとなっている。このため、TOP500のExcelシートでは、暁光のアクセラレータコア数は1984万と記載されている。

図の左右にはTCIDRAMと書かれた4つの箱が描かれているが、この部分は開発が遅れており、現在は存在していない。TCIDRAMは3D積層したDRAMチップ間を磁界結合で高速の信号伝送を行い512GB/sのバンド幅を実現する。4チップ合計では2048GB/sのメモリバンド幅を持つ計画であるが、これができていないので、4枚のDIMMの100GB/sのバンド幅のメモリしか実現できていない。

ブロック図の下辺には合計32レーンのPCI Expressと6コアのMIPS64プロセサが描かれている。

次の表は、PEZY-SCとPEZY-SC2の諸元をリストしたものである。PEZY-SCはTSMの28nmプロセスで作られ、1024計算コアであったが、PEZY-SC2はTSMCの16nmプロセスになり、2048計算コア集積している。また、MIPSの汎用64bitアーキテクチャのP6600コアを6コア搭載するヘテロメニーコアアーキテクチャのチップである。

PEZY-SCのクロックは733MHzであったのに対して、PEZY-SC2のクロックは1GHzに向上しており、倍精度の浮動小数点演算性能は、1,5TFlopsから4.1TFlopsに向上している。

PEZ-SC2チップは階層設計

PEZY-SC2はPE(Processing Element)、4PEからなるVillage、4VillageからなるCity、16CityからなるPrefectureという階層構造になっている。そしてPEZY-SC2チップは8Prefectureからなっている。

-

PEZY-SC2の最小単位は8スレッドを実行するPEである。そして、4個のPEを含むVillage、4Villageを含むCity、16Cityを含むPrefectureという階層構造でPEZY-SC2チップは8Prefectureからなっている

PEZY-SC2チップは、ブロックダイヤグラムとほぼ同じ形にレイアウトされており、次の写真のようになっている。チップサイズは27.2mm×23.7mmとなっている。

PEZY-SC2プロセサは8スレッドを切り替えて実行する

PEZY-SC/SC2の命令処理方法はちょっと特別で、1つのPEが4スレッドをクロックごとに切り替えて実行する。この方式は昔のTera社のHEPスパコンの実行方式に似ている。そして、この4スレッドの組が2つあり、どちらをアクティブにして実行するかを切り替えることができる。ActiveとIn-activeの組の切り替えは1クロックで行える。

このようなマルチスレッド実行を行うと、あるスレッドの命令が実行されると、最低でも3サイクルは別のスレッドの命令が実行されてから元のスレッドの次の命令が実行されることになる。このため、演算や条件分岐のレーテンシを(完全、あるいは部分的に)隠すことができ、実行性能を改善できるというメリットがある。

なお、PEZY-SC2 PEはMIMD(Multiple Instruction Multiple Data)アーキテクチャのプロセサであり、PEで動作する8スレッドが異なるプログラムであっても動作する。NVIDIAのV100 GPUでは、32スレッドのワープの中の各スレッドが異なる命令ポインタを使うことができるという拡張を行ったが、MIMDのPEZY-SC2は、このようなケースをV100よりうまく実行することができる。

ただし、PEの1次命令キャッシュは4KB、1次データキャッシュは2KBと小さく、これを8スレッドで共有するので、各スレッドが独立した動きをするとキャッシュミスが頻発して性能が下がる心配はある。

暁光のソフトウェア開発

暁光のソフトウェア開発にはOpenCLのPEZY版であるPZCLという言語が提供されている。そして、PEZY-SC2のPE間のバリア同期を行うsync、キャッシュのコンシステンシーを保つためのflush、スレッドのactive/in-activeの切り替え、getpid、gettidなどの機能を実行する関数が提供されている。

太湖之光では、大きなチームが作られて多くのアプリケーションが移植されたり、開発されたりしているが、暁光を始めとするExaScaler社のスパコンでは、現状は、最小限のツールが提供されて、アプリの移植や開発がなんとか進められるという状況である。そして、今回のヘテロメニーコアワークショップにおいて発表された5件あまりのアプリの開発が始まったという、初期の状況である。

その中で、電通大の山崎准教授の小脳のシミュレーションは、暁光の1万個のPEZY-SC2の内の7920個を使用するフルスケールに近いアプリケーションである。8Billion 個のニューロンを含む、猿2匹分の小脳をリアルタイムでシミュレーションすることに成功した。

エクサスケールシステムはヘテロメニーコアで実現

結論であるが、太湖之光のSW26010や暁光のPEZY-SC2はヘテロジニアス・メニーコアプロセサであり、ヘテロジニアス・メニーコアというアーキテクチャは次世代のスパコンのアーキテクチャとなると思われる。そして、ヘテロジニアス・メニーコアでExaFlopsが実現されると、その計算能力は人間の脳と同程度となる。

このような人間レベル、超人間レベルのコンピュータは、哲学、文学、神学など人間だけができると思われてきた分野にも進出していくと思われる。