Samsung Foundryに関しては2018年9月のレポートで細かく紹介したが、いくつかUpdate(と、SFF 2018では非公開だったスライド)をまとめたい。

まず7nmについて。Samsungは10月18日に、7nm EUVのRisk Productionを開始したことを明らかにした。当初は2019年からのスタートの予定だったから、2か月ほど前倒しした計算になる。TSMCも同じく10月にRisk Productionを開始しているが、タッチの差でSamsung Foundryの方が開始が早かった。

また2018年12月20日、IBMはSamsungと15年間のR&Dパートナーシップを結ぶとともに、同社のPower SystemとIBM Zシリーズ、及びLinuxOne向けのプロセッサをSamsungの7nmプロセスで製造することを発表した。

これでSamsungの7nmのLaunch Partnerとして、NVIDIAおよびIBMという2枚看板がそろったことになり、これと自社のMobile向けSoCでとりあえずVolume Productionの際にLineが空く、ということにはならなそうである。

4世代のプロセスを提供

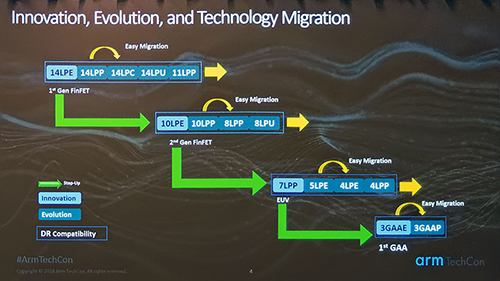

ということで、まずは同社の提供するプロセスについて(Photo10)を紹介する。同社のプロセスは大きく4つの世代に分かれる。

-

Photo10:ここからのスライドはArm TechCon 2018における"Transform Your Next Design with Complete Solutions from Samsung Foundry and Arm on 14/11/7/5nm and FDSOI"というセッションのものである

まず、14nm世代はGlobalFoundriesの14LPP/14LPEと同じ(というか、こちらにGlobalfoundriesが合わせた)ものに続き、14LPPの低コスト版の14LPC、14LPCの省電力版である14LPU、14LPPのセルライブラリ縮小版である11LPPという5つをラインナップする。このあたりは2017年に発表されている通りだ。

次がトランジスタを縮小した10LPE。これの高速版が10LPPで、SamsungとQualcommがこの10LPE/10LPPを利用したMobile SoCを製造している。これに続いてセルライブラリ縮小版の8LPPと、これの省電力版である8LPUをラインナップする。このうち8LPPに関しては、公式には発表されていないものの、Samsungが2018年11月にアナウンスしたExynos 9820で利用されていると想像される。

余談だが、Exynos 9820の前製品であるExynos 9810には、同社が独自開発したM3というコアが搭載されているが、これはデコード段6命令/cycleで12命令のIssue Portを持つOut-of-Order構成の化け物である。

Exynos 9820はこのM3の後継であるM4が搭載されており、さらに化け物じみた構成になっていると予想されるが、まぁこれは本題ではないのでここら辺でやめておきたい。

第3世代が今回のメインと7LPPである。実は2018年のロードマップだとこの7LPPに続いて6nm/5nmがラインナップされ、4nmからGAA(Gate AllAround)になるという話だった。

しかし、SFF(Samsung Foundry Forum)2018 Japanのレポートでも触れたとおり、4nmはGAAにしなくても所定のパフォーマンスが得られる目途が立ったということで、FinFETの延長となった。この結果6nmがスキップされ、5LPE/4LPE/4LPPと続くことになった。

最後がGAAで、これは3nm世代からとなっている。Samsungによればこの3GAAEを2019年に提供したいとしているが、これはプロセスそのものの提供ではなくDesign KitあるいはPDKの提供の意味と思われる。

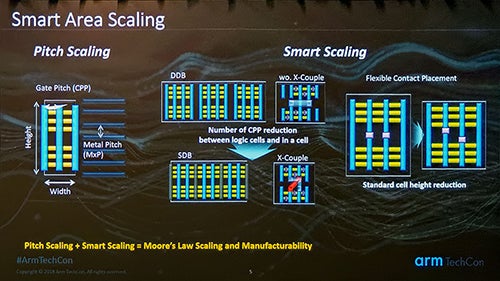

トランジスタサイズの縮小に向けて開発を進めるSamsung

Intelほどではないが、Samsungもトランジスタサイズの縮小に向けて努力している。同社はこれをSmart Scalingと呼んでいるが、例えばセルの両端にDummy Gateを設ける(=Dummy Gateが2つ並ぶ)のではなく、Dummy Gateを1本に減らすことでセルサイズを縮小するとか、コンタクトの位置をずらしてアクティブゲートにコンタクトを構築する(COAG:Contact Over Active Gate)などの工夫を導入する。

ちなみにX-Coupleについては、EUVなので斜め配線が可能で、これをM0あるいはM1に施すことで、よりセルのサイズを縮められるという意味だろう。ただ基本的にDR Compatibilityという枠に入ったすべてのプロセスは、IPやレイアウトが再利用できるように設計されており、より微細化されたプロセスに容易に移行可能、というのがSamsungの説明である。

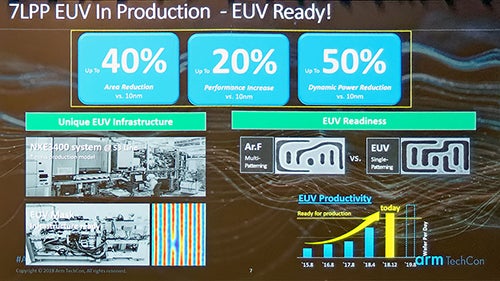

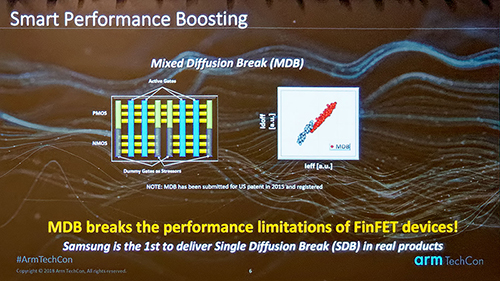

またMDB(Mixed Diffusion Break)と呼ばれる方式についても準備中(どのプロセスからこれを導入するかは明らかにされなかった)とのことだった(Photo12)。そしてEUVだが、7LPPは10LPPと比較して40%のエリア縮小と20%%の性能アップ、もしくは50%の消費電力削減が可能(Photo13)としている。

-

Photo12:要するにpMOSはSingle Diffusion Break、nMOSはDouble Diffusion Break構成とする方式。これでnMOS側にストレスを掛ける事で性能を改善するとの事

NVIDIAの次世代製品は2020年に入ってから?

TSMCのN7→N7+と比べるとずいぶん性能が大きく上がっているが、これはトランジスタや配線層の微細化なども一緒に行っているからという話であって、逆にTSMCでもN7+を10FFと比較したら同じ程度の性能改善があるから、まぁ同等という話であろう。

Volume Productionの時期とかウェハの生産量に関して、いまのところ具体的な話はないが、そもそも利用しているステッパーがTSMCと同じくASMLのNXE:3400シリーズだから、数値についてはおおむねTSMCと同等だろうし、Risk Productionの開始時期も一緒だから、Volume Productionがスタートする時期もそう大きくは変わらないだろう。

ということはやはりこちらもαサンプルが2019年の11月~12月には出てきて、βサンプルが2020年に出てくるというタイムラインになるものと考えられる。したがって、NVIDIAの次期製品は(8nmあたりの弾を仕込んでいるという噂はあるが、これが無ければ)2020年に入ってからになるだろう。

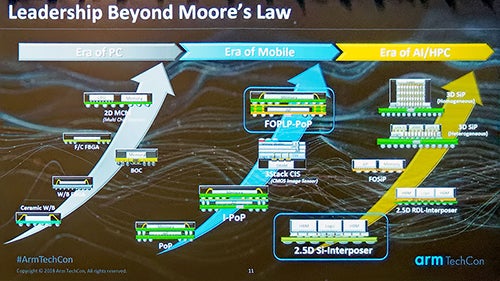

Samsungはパッケージについてもいろいろと開発を進めている。FOPLP-POPまでは実用化されており、今後は真の3D Packageに注力してゆくという話である(Photo14)。

このあたりの話は以前も出たが、このスライドのうち"3D SiP(Heterogeneous)"については、Intelの積層パッケージ「Foveros」の対抗製品(というか発表時期からすればFoverosがこれへの対抗製品)ということになるだろう。GPUではこれが利用できる部分は少ないと思う(何しろ発熱の問題が凄い)が、Mobile SoC向けには有用かもしれない。

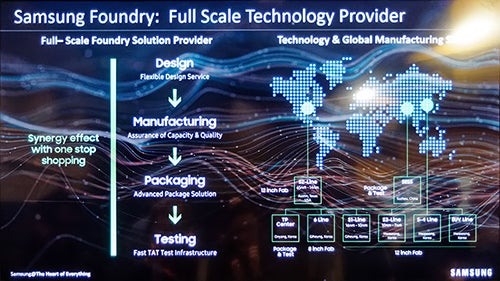

最後に製造拠点について。14nmの世代では韓国のS1とアメリカのS2の2拠点3工場で生産が行われていたが、EUVに関しては現在はS3-LineでRisk Productionを開始しており、本格生産はS3-Lineの脇に現在建造中のEUV Lineで行う方向とみられる(Photo15,16)。