次はサーバー(とCore X)である。Skylake-SPコアは14nmを利用して、最大28コアの製品まで用意されたが、この28コア製品のTDPは165W~205Wとかなり高めになっている。以前にXeon Scalableの解説でも説明したが、特にAVX512を利用する場合に猛烈に消費電力が増える。

このスライドにもあるように、SSE 4.2だと3.1GHz駆動で669W(2Pシステム全体での消費電力)なのに対し、AVXで2.8GHz/768W、AVX2で2.5GHz/791W、AVX512だと2.1GHz/767Wとなっている。

これはXeon Platinum 8180での結果だから、絶対的な性能はともかくとしてAVX512をフル駆動しようとすると、Processor base Frequency(2.5GHz)での連続稼動すら厳しいということになる。

これについては、プロセスや14nm+とか14nm++に変更すると若干改善するかもしれないが、デスクトップやノートPC向けと違って、製品のValidationに猛烈な時間とコストが掛かるXeonでは、そうちょろちょろとプロセス変更するわけには行かない。そのため、10nmにいち早く移行することで消費電力を下げようという流れは極めて自然である。

この状況に輪を掛けたのがKnights Hillのキャンセルである。プロセスの解説でも説明したが、ALCF(Argonne Leadership Computing Facility:米アルゴンヌ国立研究所の計算センター)との契約により、2021年までに1EFlopsを実現しなければいけなくなった。そもそもKnights Hillに代わるものを用意しないと、これまでXeon Phiを利用していた顧客のアップグレードパスがなくなってしまう。

そういう事情もあって、Intelは10nmが順調なら2018年中に、10nmプロセスを利用したCannon Lake-SPを投入する予定である。一方Core X向けには、Skylake-SPを14nm+(か14nm++)に切り替えたCascade Lake-Xを、第4四半期に投入する見込みである。

おそらくコア数は変わらないと思うのだが、これはAMDの出方を見ながらということになるので、もしAMDが24coreのThreadRipperを投入するなら、当然これにあわせてコア数を増やすと思われる。

Xeon PhiをXeon Scalableで代替できるのか?

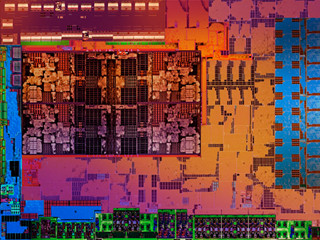

ところでXeon PhiをどうやってXeon Scalableで代替するかという話もしておきたい。現在のXeon Phi x200ファミリー、いわゆる"Knights Landing"は、SilvermontコアにAVX512ユニットを2つ、1MBの共有L2キャッシュを搭載したものを1つのTileとし、これを7×6の2D Mesh状につないだものである(Photo43)。

-

Knights Landingの構成。チーフアーキテクトだったAvinash Sodani氏は2016年9月にCavium Inc.に転職しており、Xeon Phiのチーム自身も弱体化しているという。このあたりも理由の1つと思われる

図にもあるようにDDRやPCIe Gen3やらもあるので、実際のTileは36個、72コアという構成となり、AVX512ユニットが144個ある計算だ。一方のXeon Scalableの場合、例えば28コアの構成だとこの図の右側の様になっている。コア数の違いを別にすると、次の2つになる。

- MCDRAMへのI/F。Knights LandingはこれをL3キャッシュとすることも、Local Memoryとすることもできた。

- Threadの数。Knights LandingではSilvermontベースといいつつ、1つのコアで4ThreadのSMTが実施できた。Xeon Scalableではコアあたり2ThreadのSMTでしかない。

Omni Path FabricのI/Fは標準装備(有効/無効はSKUによって異なる)だし、キャッシュ構成はちょっと異なるものの、Knights LandingはL2が1MB/Tileで最大36MB、対してXeon Scalableは28コアのものでL2が合計32MB、L3は38.5MB用意されており、むしろ余るほどだ。UPIを用意しているので複数コアの連携も簡単に実現できる。つまりXeon ScalableでXeon Phiで置き換えられるということだ。

Cannon Lake-SPによる"Knights Cove"を準備

そこでCannon Lake-SPを利用したKnights Coveと呼ばれる製品(要するにKnights Hillの代替品)が登場するとされている。構成は図1の様になるらしい。Cannon Lake-SPではDDR4 I/Fとは別にHBM2用のI/Fが搭載される模様で、通常のXeon Scalableではこれを無効にするが、Xeon Phi向けではL4キャッシュorローカルメモリとして利用できるようになると思われる。

コア数そのものは38~44コアと伝えられているが、さすがに10nm世代でもこれを1つのダイで実現するのは難しいと思われ、おそらく分割すると考えられる。コア間はUPIで接続し、片方のダイからPCI ExpressやDMIが出る形だ。読みきれないのは、Knights Landingに合わせてThread数を4まで増やすかどうかである。この辺はもうちょっと時間が経たないと情報が出てこないだろう。

このKnights Coveの登場時期は2019年といわれている。2018年中にどこまで詳細が発表されるかちょっと不明確である。Knights Coveだと性能的に1EFlopsを実現するには不足で、AuroraにはこのKnights Coveの後継であるKnights Runが入る予定である。言ってみればKnights CoveはKnights Runの前段階の検証と、Knights Landingユーザーのためのアップグレードパスということになる。