既報の通り、Intelは米国時間の7月11日にXeon Scalable Processor Familyを正式に発表、日本国内でも「Xeon Gold」シリーズの販売が開始された。製品ラインナップや特徴などはすでに紹介されているので割愛するとして、今回は内部構造に関してもう少し詳しく説明したい。

CPUコア - Skylakeコアから何が変わったか

まずCPUコアについて。"Skylake-SP"というコード名の通り、基本となるのはSkylakeコアそのものである(Photo01)。実際このレベルで見る限り、差は全くない。

このスライドによると、元々のSkylake(Photo02)からの変更点は、以下の2カ所だけである。

- L2が1MBに増量された

- Port 5にFMAが追加された

|

Photo02:Intel 64 and IA-32 Architecture Optimization Reference ManualよりSkylakeの内部構造を抜粋。ちょっと図の描き方が変わっているが、基本的に違いは見当たらない |

ちなみに筆者は、Xeon Scalable Processor Familyと同じアーキテクチャを採用するハイエンドデスクトップ向けCPU「Core X」シリーズのレビューにて、グラフ67~71の結果を基に「μop Cacheの容量が大幅に増やされた」と推定しているが、それを肯定する資料も否定する資料も含まれてはいない。

実のところIntel 64 and IA-32 Architecture Optimization Reference Manualを見ても、既存のμop Cache(Optimization Reference ManualではこれをDSB:Decoded Icacheと呼んでいる)のサイズが記載されておらず、このサイズはずっと公開しないポリシーなのかもしれない。

その他の拡張はPhoto03程度で、キャッシュ構造の変化に対応してか、キャッシュ管理命令2つと仮想化環境でのオーバーヘッド削減、あとはセキュリティ関連のみとなっている。

AVX-512ユニットの追加と消費電力

そんなわけで大きな変更としてはAVXユニットの追加が挙げられる(Photo04)。元々AVX 512ユニットは既存のPort 0とPort 1を利用する形で搭載されているが、Skylake-SPではこの外側にさらにもう1つ、AVX-512ユニットを追加した。

|

Photo04:これにより演算性能が倍増した形になる。もっともその代償がおそらくは消費電力の増加であり、このためにBase/Turboの動作周波数が3種類設定されたわけだ |

ただ、外付けで演算ユニットを追加したといっても、その演算ユニットに対してデータを渡したり、演算結果を受け取ったりするのは既存のCPU Pipelineであるので、L1 D-CacheとPipelineの帯域を倍増させたというわけだ。

前述したレビューのグラフ61を見ると、Intel Core i9-7900XのL1の帯域は、Single Threadでもピークで330GB/sec近い。

この時点でAVX-512ユニットがどの辺の周波数で動いていたかにもよるが、例えば定格の3.3GHz駆動だとすると3.3GHz×128Bytes/cycle=422.4GB/secになるわけで、330GB/secということは2.93GHzあたりで駆動していたと考えられる。

この2つ目のAVX-512が動くと"消費電力が急増する"。これはIntelも間接的に認めている。Photo05はLINPACKをSSE 4.2/AVX/AVX2/AVX-512のそれぞれで実施した場合の性能と動作周波数、消費電力をまとめたものだが、このグラフを見ると消費電力は760W~790W近辺に収まっており、一見してあまり消費電力が変わっていないように見える。

|

Photo05:760Wという消費電力はなかなか凄いが、これはXeon Platinum 8100のDual Processor構成で、メモリは384GBという重厚な構成のシステム全体の消費電力となっている。なので、例えばAVX 512で動作周波数を3GHzにしたからといって1000Wを超えるわけではないとは思う |

しかし、実際は動作周波数がSSE 4.2では3.1GHz駆動だったのが、AVX-512では2.1GHzまで下がっている。もし動作周波数を一定に保った場合にはどのくらいまで消費電力が増えるのか、ちょっと恐ろしいものがある。右の消費電力当たりのGFlopsは向上しているように見えるが、これは動作周波数を下げているから実現できているという話である。

ではAVX-512を使わなければ省電力なのか? というとこれも微妙なところ。CPUパイプラインとL1 D-Cacheのバス幅を倍増させたうえに、先のSandraのBandwidthを見るとL2も倍増に近いと思われる。こうした帯域の増加は、性能の向上にも貢献する一方で確実に消費電力も底上げしてしまう。このあたりが、Skylake-SPにおける消費電力の多さに繋がっているのではないかという気がする。

キャッシュはNon-Inclusiveに

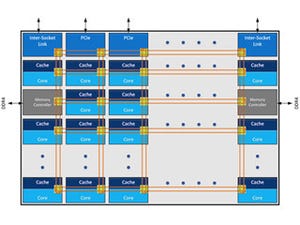

Xeon Scalable Processor Familyでは、キャッシュ周りが大きく変化した。筆者はSkylake-SPではキャッシュがExclusiveだと説明したが、実際にはNon-Inclusiveであった。何が違うかというと、Non-Inclusiveでは完全に排他でなく、場合によってはL1/L2とL3の間で共通するデータを持つ場合もあるということである(Photo06)。

どういうケースで発生するかを示したのがPhoto07になる。ある特定コアだけが使うデータであれば、L3にそれをコピーする必要は無いが、複数のコアから参照される場合に、完全にExclusiveにすると一旦L2からL3にWritebackする手間が掛かる(そしてそのコアは同じデータを再び参照する場合、もう一度L3からL2に取り込む必要がある)。Skylake-SPではこうした場合に、L2とL3に同じデータを保持することで、他のコアからのアクセスのLatencyを短縮するという仕組みの様だ。

|

Photo07:問題は「その領域が"他のコアから参照される"か否か」をどう判別するかである。この判別が甘いとL3の利用効率が落ちるし、辛いと他のコアからの参照が遅くなる。この辺りを最適に判断できるどんなアルゴリズムをIntelが実装したか、知りたいものだ |

ちなみにこの効用であるが、Broadwell-EPと比較した場合、MPI経由でのL3のアクセスは大差ないが、L2アクセスの時間が大幅に減る(Photo08,09)一方、あるLocalの1コアに着目した場合、Latencyそのものはほとんど変わらない(Photo10)とIntelは説明する。

|

Photo08:これはSPECint_rate 2006を利用して、L2/L3 Missの場合のLatencyをBroadwell-EPとSkylake-SPで比較したもの。L2 MPIとL3 MPIという表現で分かる通り、これはMP環境(通信手段はMPI)での平均的なLatencyの測定である |

まさかL3までのLatencyをcycleではなくns単位で出されると思わなかったので筆者のテストではSequentialだとcycleのみだが、In-Page Randomのこちらを見ていただくと、一応似た傾向にあることが分かる。もっともcycle数で見るとこちらの様に、もう少し差が広がっている。