米Western Digitalは6月27日(現地時間)、96層3D NANDチップ「BICS4」の開発に成功したと発表した。2017年下半期からOEMに対してサンプル出荷を、2018年中に量産開始を予定するという。

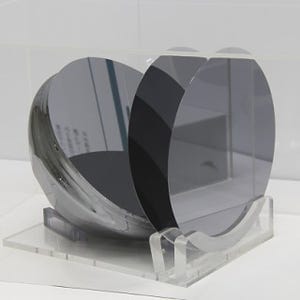

BiCS4は、Western Digitalと東芝メモリによる共同開発とされ、3ビット/セル(TLC)および、4ビット/セル(QLC)で提供される。東芝メモリからもQLC技術を用いた3D NANDに加えて、96層3D NANDについて発表している。

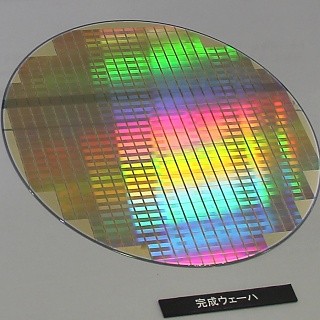

これによると、64層と比べて単位面積当たりのメモリ容量を約1.4倍に大容量化したほか、チップサイズを小型化することで1枚のシリコンウェハから生産するメモリ容量を増やし、bitあたりのコストを削減できるとしている。エンタープライズ向けやPC向けのSSD、スマートフォンやタブレット向けのストレージ、メモリカードなど市場のニーズに合わせて製品を展開する。

また、Western Digitalは日本国内における東芝との「合弁製造施設」について、事業をの継続性を強調する。同社によると、2017年に供給される3D NANDのうち、64層3D NANDチップ「BICS3」が75%を占めるとの見通しを立て、東芝・Western Digital陣営が競合よりも高い割合になるとしている。