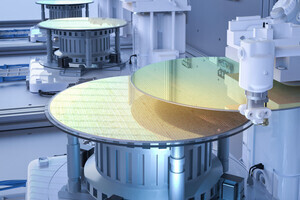

Cadence Design Systemsは3月13日(米国現地時間)、TSMCのシリコンウェハの先進的パッケージング技術「InFO(Integrated Fan Out)」をサポートする包括的に統合された設計フローに新たな最適化機能を追加したことを発表した。

今回、新たに統合されたフローでは、モバイル、IoTアプリケーション向けに設計・検証機能、およびダイ間接続のモデリング技術が提供されるほか、以下のCadenceのツールおよび技術が含まれ、これにより、SoC設計者は、1つのキャンバス上でマルチファブリックを扱うことができるようになり、システム全体設計の視点で複数ダイとInFOパッケージ間のネットリストを生成することが可能となるほか、パッケージ・デザイン・データベースからStandard Parasitic Exchange Format(SPEF)を直接生成し、タイミングサインオフの効率化を図ることが可能となった同社では説明している。

- OrbitIO interconnect designer

- System-in-Package (SiP) Layout

- Quantus QRC Extraction Solution

- Sigrity XtractIM technology

- Tempus Timing Signoff Solution

- Physical Verification System (PVS)

- Voltus-Sigrity Package Analysis

- Sigrity PowerDC technology

- Sigrity PowerSI 3D-EM Extraction Option

なお、TSMCでは、同フローを用いることで、小さなフォームファクター内で帯域幅を拡大させることが可能になるとしているほか、Cadenceのデジタル設計、サインオフ検証、カスタムIC設計テクノロジーがすべて含まれているため、現在のマーケットニーズに対応することが可能になるとコメントしている。