次がHot Joinである(Photo07)。Hot Plugと違うのは物理的に着脱されることは想定していない。むしろ省電力のために、あるデバイスをばっさり電源オフにして、必要な時にオンにする、なんてシナリオで動的にデバイスのJoin/LeaveをI3C自身が管理できるようになった。

細かいところではエラー検出/回復の仕組みが追加されたほか、In-band CCC(Common Command Codes)が提供されるようになった(Photo08)。このあたりは、I3Cが「普通の」I/O Busっぽく進化している感じである。元々は、こういう手順が必要無い簡単な接続方式、ということで登場したのがI2Cだったが、昨今の使われ方だとそれだけでは足りなくなっている、という実情が反映されていると思える。

ちなみにI2Cとの互換モードであるが、50nsのSpike Filterが必須になったほか、Clock Stretchingが禁止になっている(Photo09)。Clock Stretchingは、デバイス(Slave)側の処理が間に合わない場合に、SCLを強制的にLowに落としっぱなしにすることであるサイクルを引き伸ばし、その間に処理を行うという技である。Open-Drainだったからこそ可能な技法であるが、I3CではSCLがPush-Pullになったので、もうこの技法は使えないことになる。

|

|

Photo09:50nsのSpike Filterは現在のI2Cでも時々使われる。実装は色々あるようで、RC回路で構成した例を筆者は知っている。ちなみに100nsのSpike Filterを実装したケースも見たことがあるのだが、これだと12.5MHz駆動に支障がありそうな気がする |

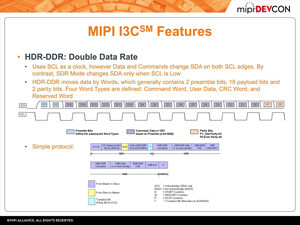

次に高速転送モードの話をしよう。SDRは先ほどPhoto05で示した形だが、HDR(High Data Rate)では倍速の転送が可能になっている(Photo10)。SDRとHDRの切り替えはMaster側から特定のビットパターンを送ることで実現する形だ。この特定のビットパターンはI2Cデバイスからは認識できないので素直に無視される。なので、I3Cデバイスのみがこれを利用できる仕組みだ。そのHDRモードの基本は、HDR-DDR(Photo11)である。これはSCLの両エッジを使ってデータを送るというDDRの基本で、これにより転送速度は12.5MHzの場合で25Mbpsになる計算だ。

|

|

|

Photo10:Photo08に出てきたCCCを使ってEnterHDRxを送ることで、以後I3CはHDRモードに切り替わる。ここから抜けるには、ホストからHDR Exit Patternを送る形で、これが送られたあとはSDRモードになる |

Photo11:HDR-DDRではCRCも付加される |

ただHDR-DDRだけでは単に2倍にしかならない。そこで次に出てくるのがHDR-TSP/TSPである。TSPは"Ternary Symbol for Pure bus"の、TSLは"Ternary Symbol for Legasy-inclusive-bus"の略である。まず最初にHDR-TSPの方を説明すると、これはSDAとSCLの両方を使って、1cycleに3値のSymbolを送る(これがTernary Symbolの意味)仕組みである。具体的には

| Symbol | SCLが変化 | SDAが変化 |

|---|---|---|

| 0 | Yes | Yes |

| 1 | Yes | No |

| 2 | No | Yes |

となる。これを12Symbol分送ると16bitのデータ+2bitのパリティに相当することになり、これとHDR-DDRを組み合わせることで12.5MHzの場合に33.33Mbpsの転送レートになる計算だ。

ただこのSymbolは、I3Cデバイスのみに使える方法で、I2Cデバイスには利用できない。そこでI2Cデバイスと互換性を持たせたのがHDR-TSLとなる。といってもSymbolそのものに違いは無く、速度制限が付くだけである。HDR-TSLではクロックが10MHz「以上」でないといけない。これは何故か? というと、先のPhoto09のSpike Filterに関係してくる。そもそも既存のI2CデバイスはTernary Symbolをサポートしないから、これを利用している間はI2C Busの信号を無視してくれることが必要になる。そこでSCLがHighの時間を40ns以下に抑えると、Spike Filterを利用することでI2CデバイスはSCLがHighであることを認識できず、SCLが常にLowであると判断してくれる。この「SCLがHighである時間を40ns以下にする」ためには、クロックを10MHz以上にしないといけない、という訳だ。

とりあえず現状は仕様書が出たほか、Cadance/SynopsysなどのIPベンダがすでにI3CのIPの提供を開始している。シリコンレベルで言えば、まだこれを実装した最終製品は存在しないが、先のIPをFPGAに組み込む形での検証などはすでにスタートしている。国内では立野電脳のIdreic DIMM I3C I/Fアダプタが2017年第2四半期にリリース予定という程度だが、このあたりは追々増えてゆくと思われる。

ただI3Cのコントローラの規模は、MIPI Allianceの想定では2000ゲート未満、ということであるが、I2Cの場合は1000ゲート程度で実装しているIPも少なくない。その意味では、スマートフォン向けのSoCにこれを組み込むのは容易だが、8bitの小型MCUや低価格センサに2000ゲートを突っ込むのはちょっとコスト面でまだ苦しいかもしれない。またI2Cに比べるとホスト側で行うべき処理が確実に増えており、ソフトウェアスタックがやや重くなる事も必須である。なので当面はスマートフォン/タブレット向けのSoCにまずコントローラが入るだけといった形で、MCUあるいはセンサ類が対応するのはちょっと先になりそうだ。そんなわけで、緩やかに立ち上がってゆくという感じになるのではないかと思う。