次の図は、VGG16、GoogLeNetとSqueezeNetをFP32、FIXED-16とFIXED-8で計算した場合の精度を示す表で、16bit整数と8bit整数の場合は、再学習した結果も載っている。

VGG16のTop5ではオリジナルのFP32が86.64%であるのに対して、FIXED-8で再学習すると88.06%と1.4%余り改善している。一方、GoogLeNetのTop5では88.65%が85.7%と3%近く低下している。SqueezeNetでも81.37%から80.35%と約1%低下している。ということで、この結果をどう見るかは微妙であるが、この図のタイトルでは、8bitで十分と主張している。

|

|

|

VGG16、GoogLeNet、SqueezeNetのTop1とTop5の精度をFP32とFIXED-16、FIXED-8で計算した場合の精度。この結果は微妙であるが、図のタイトルでは8bitで十分と主張している |

次の図の中の表は、GoogLeNet、SqueezeNet、VGG16の画像認識の上位5候補のリストであるが、1位はすべてShetland Sheepdog、2位もCollieで一致している。また、右側はFP32とFIXED-8でのオブジェクト認識の結果で、FP32の場合は自信が0.98に対して、FIXED-8の場合は自信が0.78に下がっていが、どちらも認識したオブジェクトはほぼ同じである。

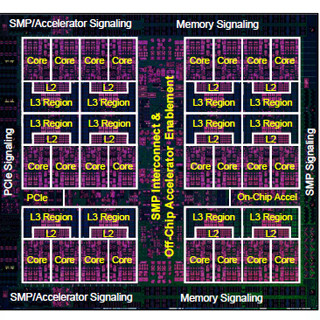

CNN用のアクセラレータであるAristotleは、5cm角のボードにXilinxのZynq7000シリーズのFPGAを搭載している。ZynqシリーズのFPGAの集積度の大小で、1PEから12PEまで搭載できるPE数が変わる。

AristotleアクセラレータのPEは、データと重みを掛ける畳み込み計算部の次に総和を求めるアダーツリーがあり、さらに、非線形のReLU、最大値や平均値をとるプーリングユニットがある。これ自体は普通の構造である。ただし、ダイナミックに精度を変えられるという特徴がある。

コンパイラは、Caffeモデルとハードウェアのパラメタから、どのようにハードウェアを動かすかのスケジューリングを行い、PEの命令を生成する。生成された命令はDRAMに格納され、アクセラレータに渡されて実行される。

LSTM用のDescartesアクセラレータの疎行列を扱う部分は、FPGAではうまくフィットせず、「EIEチップ」と言うASICを作っている。この部分は10.13MBのSRAMと64個の乗算器を持ち、800MHzのクロックで動作する。残りの部分は、Xilinxの「Kintex UltraScale KU060 FPGA」と「KU115 FPGA」で作られている。

Descartesアクセラレータは、LSTM用であり、任意の行列サイズ、任意の層数を扱うことができる設計になっている。スレッドあたり16/32/64 PEとスケーラブルな設計で、バッチモードと非バッチモードで動かすことができるようになっている。バッチモードは入力をまとめて処理するので、スループットは高いが、結果が出てくるまでの時間が長い。非バッチモードは入力を1つずつ処理するので、スループットは低いが、結果が出るまでの時間は短い。