EUV露光用のレチクル表面に付着する欠陥数(レチクルをEUV露光装置に脱着するたびに増加する92nm以上のパーティクルの数)は、2010年以降、毎年1桁ずつ減少を続けており、今年は、0.001個レベルを切る見込みだが、顧客は、量産時にはペリクル(レチクルにゴミがつかないように、レチクルを覆うようにかぶせた透明保護膜)なしでもう1桁少ない値(0.001個/レチクル)を要求している(図3)。

このため、EUVリソグラフィでも、従来のリソグラフィの場合と同様に、ペリクル膜を採用してレチクルへのパーティクル付着を防止することになろう。ASMLでは2012年より研究協業パートナーとともにEUVリソグラフィ専用のペリクル膜の開発にも取り組んでいる(図4)。ペリクルは、真空引きやベントの際に損傷せず、真空中や水素雰囲気中でも劣化せず、有機ガス放出が規定数値以下で、装着しても露光性能に影響を与えないものでなければならない。現在、透過率は85%だが、目標は90%に置いている。

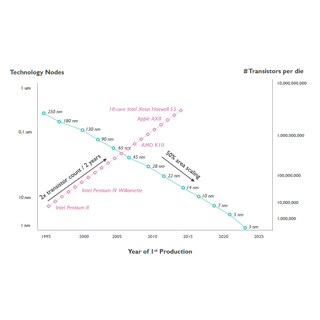

Wennink氏は図5に示すように、ロジックデバイスの技術ノード22nmから2nmに至る詳細なEUVリソグラフィ装置ロ―ドマップを示した。レンズ開口数(N.A.)は、現在の最新機種では0.33だが、5nm以降では0.5より大きく引き上げる必要があろう。それができなければ、N.A.=0.33のままダブルパターニングを併用する必要があろう。重ね合わせ精度も表示のとおり改善させていく。

多くの業界関係者の最大の関心事であるスル―プットについては、表の最下段に示す。スル―プットは、極端紫外線ド―ズ量(mJ/cm2)次第であり、つまり光源出力をどこまでひき上げられるかにかかっている。現在、80Wになったばかりだが、7nm世代までには250W、 5nm世代には500Wへ引き上げることを目標にしている。そして、7nm世代でのスル―プットは毎時125枚(300mmウェハ)、5nm世代では165枚を開発目標にしている。

著者註:2015年6月3日に東京で開催されEUVL基板開発センター(EIDEC)の年次報告会の席上、ASMLチーフテクノロジストSVPのWilliam Arnold氏は直近の実績と目標を以下のように具体的に示している。

光源出力 スル―プット 生産性 2014年 80W >55枚/時 >500枚/日 2015年 125W >75 >1000 2016年 250W >125 >1500 EUVリソグラフィは光源出力がなかなか計画通りには上がられないことが最大のボトルネックとなっており、このため、ASMLは、世界最大のリソグラフィ光源メーカーであったCymerを買収したが、顧客の要求通りには開発が進んでいないと多くの顧客が不満を漏らす。リソグラフィ専門家のなかには、EUVリソグラフィの将来に悲観的な見方を示すものも少なくない。ニコンのように「EUVリソグラフィは筋が悪い」(牛田社長)とEUVには手を出さない装置メーカーもある。

ASMLのEUVリソグラフィのグローバルな開発協力体制を図6に示す。顧客として、Intel、Samsung Electronics、TSMC、SK Hynix. 東芝の5社が上がっている。共同開発パートナーとしては東京エレクトロン、ソクド、HOYA、住友化学、JSR(の子会社)など日本の装置・材料メーカーが名をつらねており、日本勢の協力が大きいことがうかがえる。欧米の多数の大学や研究機関との共同研究も盛んに行われている。

著者註:先にニューヨーク州立大学(SUNY)Polytechnic Institute(ニューヨーク州Albany)に吸収されてしまったSematechの名前が消えており、SUNYの名前も見当たらない。そのキャンパスで次世代プロセスを開発するIBMの名前もない。一方、imecとASMLは両社の1988年以来の長年の協業をさらに発展させ、2013年秋にimecキャンパス内に共同でAdvanced Patterning Centerを開設した。今後のリソグラフィはウェハプロセス依存性が大きいため、ASMLのリソプロセス研究陣が先端ウェハプロセスの行えるimecに移動し、7nmおよびそれ以降のパターニングの実用化に共同で取り組んでいる。