富士通研究所は6月13日、次世代サーバに搭載されるCPUなどのチップ間データ通信において、毎秒56ギガビット(Gbps)の高速データを受信可能な受信回路を開発したと発表した。

近年、サーバのデータ処理能力の向上が求められるなか、CPUの高性能化とともに、CPUなどのチップ間のデータ通信速度の向上も期待されている。

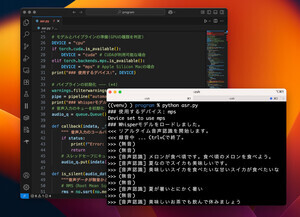

そこで、同社は受信回路の高速化には、劣化した入力信号波形を補償する回路「DFE」の処理能力向上が有効として、新たなアーキテクチャ「先読み回路」を開発した。

56Gbpsの通常の回路設計において、DFEは16個を連結させて用いるが、4個の場合は4分の1の周波数で動作させる。これより、56Gbpsの場合、4分の1の周期は71ピコ秒となり、半分の2ビット分の補正までしか収めることができず、タイミングエラーとなっていた。

同社は今回、1ビット前の選択結果から得られる候補2つをあらかじめ計算しておき、2ビット前のビット値が決定すると1ビット前のビット値と現在のビット値が同時に決定することで並列処理が可能な先読み方式を考案した。これにより、演算時間が短縮されるため、56Gbpsで動作する受信回路の開発に成功した。

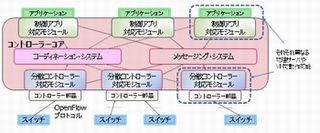

同技術により、次世代サーバやスーパーコンピュータ内でCPUの性能が倍になっても、ピン数を増やすことなくCPU間通信を広帯域化することができ、CPUを多数接続した大規模システムでの性能向上に貢献することが期待される。

加えて、同技術によって光モジュール通信の規格であるOIF標準規格への対応も可能になり、OIF-CEI-28Gの光モジュール通信で400GbpsEthernetを構築する場合に比べて並列動作する回路数(レーン数)を半減できるため、光モジュールの小型化による低電力化やシステム全体の高性能化も期待される。