Lattice Semiconductorは5月23日に、同社CEOであるDarin G. Billerbeck氏(Photo01)を招いての経営および技術戦略の説明会を開催した。Billerbeck氏自身は1月に来日されているし、新製品は今年4月に発表したばかりであり、今回はそんな新しい発表とかは特になく、専ら業界動向や同社の動向について質疑応答を行う会見となった。

そんなわけで、本題に入る前に、まずは同社の状況について。同社の第1四半期の業績は4月24日に発表されたが、その概要がこちらである(Photo02)。

特にこの1年余りは好調であり、今年第1四半期は売り上げの最高記録を達成している(Photo03)。損益の詳細がこちら(Photo04)であるが、粗利益が56%とかなり高くなっているのは「この業界では優秀な成績だと思う」(Billerbeck氏)との事だった。

|

|

|

Photo03:今年の年間収益は3億6000万ドル程度を予定しているとの事。ちなみに題名は収益推移になっているが、これは売上推移だと思う(英語版ではQuarterly Revenueになっている) |

Photo04:粗利益は50~55%の範囲と推定していたとの事 |

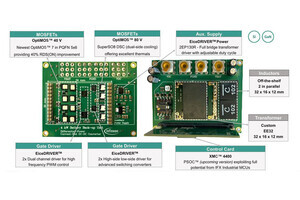

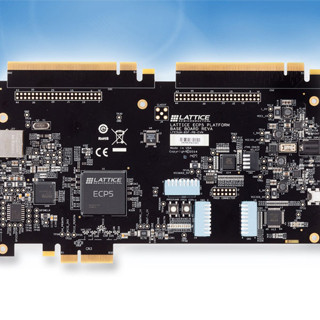

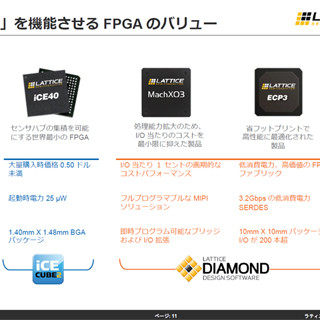

さて、製品群としては3種類のFPGAがメインとなる(Photo05)のは変わっていない。ちなみに後の質疑応答で出てきた話として、ではこの2014年Q1の売り上げの比率は?というものとして

- 38~40%がCommunication。ここではMach XO/XO2とECP3がそれぞれ1/3ずつ売れている。

- 33~34%がConsumer向け。Tablet向けはice40とMach XO2 ZE、一方Smartphone向けはice40のみ

- 残りがIndustrial向けで、ここではすべての製品が利用される

という話であった。また日本のマーケットは特に重要であり、それは日本の顧客が従来の様に新規のASICを製造するのではなく、既存のASICやASSPを引き続き使いつつ、差別化や新機能の追加などをFPGAを使って実装する方向にあるからだ、という話であった(Photo06)。

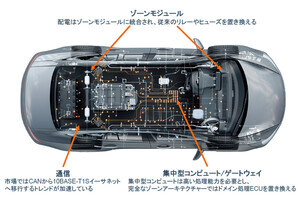

さて、ここからが本題。こうした話の後で、突如として出てきたのがこのスライドである(Photo07)。

これまで、「低コストなSolutionを提供しようと思った場合、40nmがBestであって、28nmはやや高くつく」としてきたBillerbeck氏だが、LUT数の要求が次第に増えてゆくと、どうしてもプロセスの微細化は避けて通れない。また、Static PowerはともかくとしてActive Powerに関してはやはり微細化が省電力化には有利である。こうした事を踏まえて、2015年にはまず中間的なソリューション、そして2016年には28nmプロセスを利用した製品が投入されるという話である。

まずその中間的なソリューションとは何か? という話だが、プロセスそのものは40nmに留まりつつ、28nmで予定している機能(一例として挙げられたのが、何とPower Gatingだった)を実装したものになる、という話であった。このあたりは、開発ツール側の対応とマッチさせつつ、まずは諸々の新機能に対応した開発ツールと、これを40nmノードで実現した製品を投入し、次に28nmノードの製品に切り替わってゆくというストーリーと思われる。

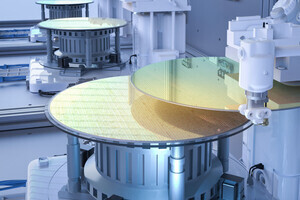

その28nm、今の時点では「どこのFoundryを利用するかは言えない」という話であった。2016年にサンプル出荷だとすると、2015年中にTape outすれば間に合う事になる。この観点からするとTSMC/GLOBALFOUNDRIES/UMC/Samsung/SMICといったFoundryが全部量産可能になっている「筈」で、現在は品定めをしているというあたりだろうか。ただヒントとして「現在の」Foundryが28nm向けに提供しているProcessはどれも余り良いSolutionではない様に思うとの話だった。実際Latticeは低消費電力・低価格を志向しており、一方現在の28nmはLPであっても結構高速に動作する、やや消費電力の高いプロセスだからで、このあたりは今後各Foundryがどんなプロセスのオプションを出してくるか次第なのかもしれない。

余談ながらFinFETについては「(うちのFPGAに使うには)FinFETは高価で、しかも消費電力が多すぎる」とのことだった。これに関連して氏が示したのがこの図である(Photo08)。これを見ると、なるほどECP4がなくなった理由がわかるという気はするが、それはさておきここで氏が示したのは、TSMCの28nmで製造されるKintex 7のコストが、傾きこそ低い(ECP5並)ものの、初期コストが他の製品よりずっと高くなることで、つまりある程度のLUTを搭載する、大きなFPGAでないとペイしにくいということである。このあたりをどう解決するのか、というのが同社における大きなチャレンジになるようだ。

ところで同社の場合、一番小さいパッケージだと1.4mm×1.48mmとかになる(Photo09)。こうなってくると、微細化をしてダイサイズを半減させた場合、Pad Limitとかが効いて来てしまう。これについて氏は「例えば現在1K LUTを搭載する品があったとして、これが28nmになったらどうなるか? というと、LUTを2Kにするというのが 1つのアイディア。もう1つは1KのLUTに加えてマイコンを内蔵するという可能性もある」と示唆した。ただ同時に「マイコンを内蔵させるには、膨大な開発費がかかる事になる。なので、こうした構成が大量に要求されるKiller Applicationがあれば考える」(つまり、Killer Applicationが見当たらなければ、MCU内蔵のアイディアはない)という返事であった。

という訳で、図らずもLatticeの次世代製品に関する詳細が多少明確になった記者説明会であった。