--ただ、そういった分野のエンジニアやシステムエンジニアはFPGAを扱ったことが少ない、というよりもHDLやVelirogを使える人が少なく、RTLが書けないという課題がありますよね?。むしろ、いつまでそういった言語を使わせるんだ、と。

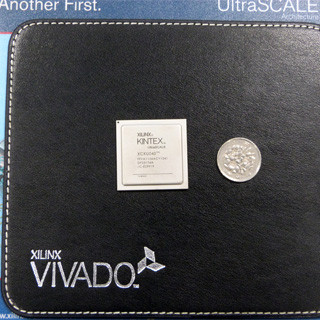

Rogan:我々もそれは理解していて、開発ツールである「Vivado」にてCコードベースの設計を可能とする「Vivado HLS」を提供することで、そうしたニーズに応えようと取り組んでいます。

--Cコードで設計ができるとなると、ユーザーの層も一気に拡大できますね。最近はMakeに代表されるような場所で、ソフトウェアエンジニアがハードウェアを活用するといったシーンも広がってますので、そうした流れにFPGAも乗ることができるようになる?

Rogan:FPGAのユーザーがハードウェアエンジニアからソフトウェアエンジニアに広がって行っているのは我々も感じてますね。我々のCEOはテクノロジドリブンの人で、提供するツールにしてもEDAツールベンダが提供するものと互角の性能を出せるものを、ということでVivadoが開発されました。

--そういえばMATLAB R2013bでVivadoの前のツールであるISEと組み合わせて手軽に回路構築ができる発表もありましたね。

Rogan:あれば主に通信分野のユーザーを楽にしたいということを目指した取り組みですね。

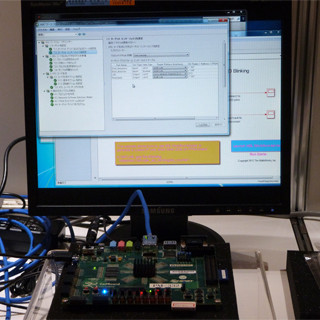

--実際にMATLAB EXPOの会場でデモを見ましたけど、コードを読み込ませるだけで、あっという間に回路が構成されたのは驚きでした。今までの、高位言語とHDLでやり取りして、回路を見て、とかいう面倒なやり取りはなんだったのか、というくらいのインパクトでした。

Rogan:同じような取り組みとしてはNational Instruments(NI)のLabVIEWと組んで産業機器向けに提供していることですかね。

--NIやMathWorksは別として、開発ツールもサードパーティに任せずに関係も自前で手掛けるとなると、デバイスの開発コストに加えて、そういったコストも必要になってきます。プロセスの微細化による設計コストの増加を考えると、結構な負担になりませんかね?

Rogan:Xilinxの売り上げは20億ドル強あり、R&D費用にその20%を費やしています。競合メーカーも同じように売り上げの20%をR&Dに費やしていますが、売り上げ規模そのものが我々よりも幾分低いので、同じようなことができるとは思っていませんし、もし同じようにデバイスの開発を続けていったとしても、どこかで妥協が出てくると見ています。

また、我々は40nmプロセスまではUnited Microelectronics(UMC)をファウンドリとして使ってきましたが、28nmプロセス以降はTSMCに移りました。そこで学んだのは、TSMCのプロセスの凄さですね。おかげで先端プロセス製品は国内でも評価が高く、そういった意味ではAlteraとのシェアも良い数字になってますね。