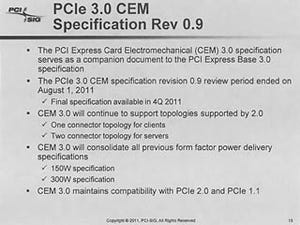

PCIe 3.1

前回予定されておらず、今回新たに追加されたものがこちら。PCIe 2.1の時と同様に、既存のPCIe 3.0のSpecificaitionに、拡張機能として追加されたECNを全部包括したものがPCIe 3.1とし標準化されることが明らかになった。追加されるものは全てECNの形で既に提示されているので、その意味では新しいものは無いとも言えるが、この中でPCIe L1 PMは割と大きなインパクトを及ぼすとPCI-SIGは考えており、なのでPCIe L1 PMをサポートしていないPCIe 3.0と明確に区別する目的でPCIe 3.1をリリースすることにしたそうだ。

さてそのPCIe 3.0であるが、消費電力/性能/機能の3つの分野でそれぞれ変更がある。まずPowerは、

・M-PCIe

・L1 PM Substates with CLKREQ

の2つ。Performanceは、

・Enhanced DPC

・Lightweight Notification (LN) Protocol

の2つ。そしてFunctionalityでは、

・Precision Time Measurement

・Separate Refclk Independent SSC Architecture (SRIS)

・Process Address Space ID (PASID)

の3つが主要な項目である。ちなみにECNそのものとしては他にも、

・Change Root Complex Event Collector Class Code

・Downstream Port Containment (DPC)

・8.0 GT/s Receiver Impedance

・PASID Translation

・End-End TLP Prefix Changes for RCs

が既に公開されており、これもPCIe 3.1に盛り込まれる予定だ。

細かい仕様はそれぞれのECNを見ていただくのが早いが、この中で一番インパクトのあるL1 PM Substates with CLKREQについてちょっと説明する。端的に言えば、Linkが構成されており、ところが通信が行なわれていないIdle状態の場合に、更に消費電力を下げる仕組みである。もともとPCI ExpressにはL1というステートがオプション扱いながら存在しており、これは復帰までややLatencyが大目に掛かるものの消費電力が少なくなるという、いわゆるスタンバイ状態であった。ECNではこのL1ステートをL1.0/L1.1/L1.2という3つのサブステートに分解している。

|

Photo14: 既存のPCIe(水色)が、2015年あたりで更にカクっとするのは、このあたりでPCI Express 4.0がリリースされることを想定しているためだろう。ただDesktop/Notebook向けと違い、基幹サーバー系のバックプレーンなどでは比較的長期間メンテされるので、2016年の時点でもまだ若干は残ると想定しているようだ。 |

L1.0は従来のL1と全く同じ動作をする。L1.1はやや省電力にするもので、Linkのcommon mode voltageは維持するものの、Upstream/Downstreamの状態を確認する機能を無効化してよい(つまり自分の上下に繋がるデバイスの状態を確認しなくて良い)となるもので、L1.2ではこれに加えてLinkのcommon mode voltageも維持する必要がなくなる。つまり電気的にPHYをShutdownできることになる。これにより、待機中のPHYの消費電力を大幅に削減できるというもので、"Ultrabookの様な製品では特にこれが効果的であると思う"(Yanes氏)という話であった。勿論このECNは5月31日にFinalizeされたばかりなのでまだ実装例は無いが、先ほどのCadenceのプレスリリースにもあるように、既にSolutionやIPを提供するベンダーは存在しており、PCI-SIGとしても2014年以降はこのL1 PM Substatesをサポートしたプラットフォームが圧倒的に増えるだろうと予測しているようだ。

ちなみに仕様にもあるCLKREQであるが、これはCLKREQ#という信号線(これが元々Option扱い)を使って、L1.0とL1.1/L2.2の遷移を制御するためで、なのでもしまだCLKREQ#を実装していない場合、L1 PM Substateの実装に当たってはCLKREQ#を追加する必要がある。

ついでに、先ほどOCuLinkのところで出てきたSRISの話も簡単に。元々PCI Expressではオプション扱いとしてSSC(Spread Spectrum Clocking:スペクトラム拡散クロック)をサポートしているが、送信側と受信側で別々にReference Clockを用意し、しかもそれがSSCなケースがSRISとして取り扱われる(Photo15)。OCuLinkはこのSRISに対応する、というのが先に出てきた話である。実のところECNを読むと、これまで仕様的にはSRISが可能ではあったが、実際にインプリメントするために必要な情報が含まれていなかったので定義したとあり、OCuLinkの実装にあわせてこのあたりを充実させたと考えるのが妥当だろう。

|

Photo15: SRISの模式図...の筈(これはECNから抜粋)なのだが、その直前に説明されているSRNS(Separate Refclk With No SSC)と図版の番号も一緒だったりする。勿論構成そのものは同じで、あとはTx PLL/Rx PLLを生成する際にSSCにするかしないかだけ(つまりH1(s)とH2(s)の中身だけ)が違いだから、図が一緒なのは正しいのだが。 |

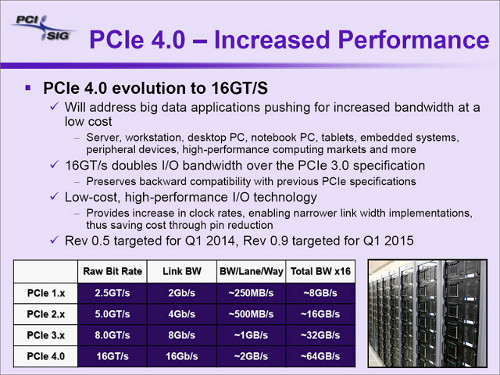

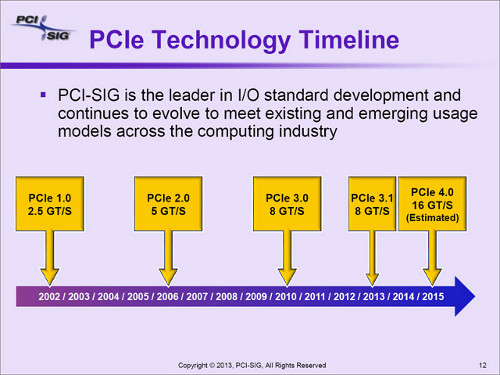

PCIe 4.0

最後がこちら。昨年の段階では、まだ具体的なSpecificationのRevisionが出てこない(0.3以前の、おそらく0.1とかその位)状態だったが、現在はもう少し順調に進んでおり、Revision 0.5が2014年第1四半期、Revision 0.9が2015年の第1四半期とされている(Photo16)。こちらに関しては今のところ順調であり、既存のCEM(Card ElectroMechanicl) Specificationそのままで16GT/secが実現できる見込み、という従来の見通しがそのまま語られた程度に終わった。

また一応見通しとしては2015年中にFix(Photo17)という話であったが、Gen 3のときもRevision 0.7からRevision 0.9に行く前にRevision 0.75が挟まったりしたので、今回もスムーズに行くかどうかはちょっと微妙なところ。また10inchを超える配線を使う場合のRepeaterに関しても特に話がなく、このあたりはまた次のIDFのあたりで確認したいと思っている。